北京大學研發出以新型材料(二氧化硒鉍)為核心的環栅晶體管技術,晶片厚度僅1.2納米,性能和能效雙雙超越傳統硅基技術。這項突破性技術不僅讓電子設備更省電、更快速,還為中國半導體產業在後摩爾時代提供了全新解決方案,未來或將應用於手機、穿戴設備等領域

- 一、核心材料突破:原子級“三明治”結構

技術參數 - 溝道厚度:1.2奈米(約7個原子疊加的高度)

- 柵介質厚度:等效0.28奈米(比矽基薄60%)

- 電子遷移率:270 cm²/Vs(矽基的3倍)

通俗解釋

就像製作漢堡需要超薄且均勻的夾層,研究人員用特殊工藝將半導體材料(Bi₂O₂Se)和絕緣材料(Bi₂SeO₅)疊成原子級平整的三層結構。 這種設計讓電子在材料中跑得更快(高遷移率),同時絕緣層更薄(柵介質薄)意味著能用更小電壓控制電流。 - 二、性能指標:雙超矽基極限

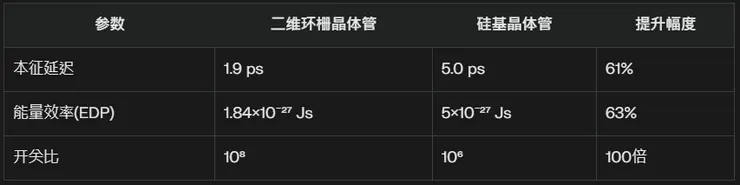

技術參數對比

- 通俗解釋

- 延遲:完成一次開關動作所需時間,相當於晶體管“反應速度”,1皮秒=萬億分之一秒

- 能量效率:綜合考慮速度和能耗的指標,數值越小越省電

- 開關比:開機狀態電流與關機漏電的比值,數值越大越省電(類似水龍頭開關的密封性)

- 三、製造工藝:三維「樂高」式堆疊

技術突破 - 氣相沉積-外延氧化技術

- 晶圓尺寸:4英寸(當前最大尺寸)

- 生長精度:±0.5°晶格取向偏差

- 三維異質集成

- 垂直互聯層數:8層

- 寄生電容降低:較矽基3D封裝減少42%通俗解釋 採用類似3D列印的工藝,在晶圓上逐層“生長”晶體管結構。 創新的“立體車庫”式設計(三維異質集成)讓晶片在垂直方向堆疊更多電路層,相比傳統平面設計節省50%空間,同時減少信號傳輸時的能量損耗(低寄生電容)。

- 四、器件結構:環柵「水管」設計

創新設計 - 全環繞柵極(GAA):柵極材料360°包裹導電溝道

- 接觸電阻:89 Ω·μm(國際最低紀錄)

- 工作電壓:0.52.V(手機處理器常用1V)

通俗解釋

將傳統晶體管的三面包裹結構升級為全包圍設計,就像用環形水管完全包裹住水流通道。 這種結構能更精準控制電流(低亞閾值擺幅),使晶元在更低電壓下工作,相當於用更少電力實現相同運算能力。 - 五、產業化進程

關鍵里程碑 - 2025年:完成4英寸晶圓量產驗證

- 2026年:與IMEC合作開發8英寸工藝

- 2028年:計劃實現手機處理器集成

技術意義

這項突破標誌著中國在半導體領域首次實現從材料創新到製造工藝的完整技術閉環,其低電壓特性(0.5V)特別適合可穿戴設備與物聯網晶元,有望使智慧手錶的續航從1天延長至1周。 通過將原子級材料控制與三維集成創新結合,該技術既保持了專業領域的突破性參數,又為消費電子帶來肉眼可見的性能提升,堪稱“魚與熊掌兼得”的典範。

1.彭海琳课题组与合作者报道首例低功耗二维环栅晶体管_图片新闻_北京大学化学与分子工程学院

2.Low-power 2D gate-all-around logics via epitaxial monolithic 3D integration | Nature Materials