Chiplet 是實現異質整合的一種方式:指將不同功能(如 CPU、GPU、記憶體、SerDes)以獨立小晶粒製作後再整合成系統。

隨著算力需求持續攀升,晶片面積越做越大,製程也愈加先進與昂貴。這讓過去仰賴摩爾定律的經濟模型開始失靈。傳統的 SoC(System on Chip,系統單晶片)設計,將所有功能整合在單一矽晶片上,雖然方便,但一旦面積變大、良率下降,成本就會失控。

Chiplet 提供了一種解法:將不同功能模組事先製作成小晶片單元,再透過封裝技術組合起來,形成一個完整系統。這種分模設計,讓系統變得更模組化,也更容易根據需求調整。連大廠也轉向:市場與技術共同推動

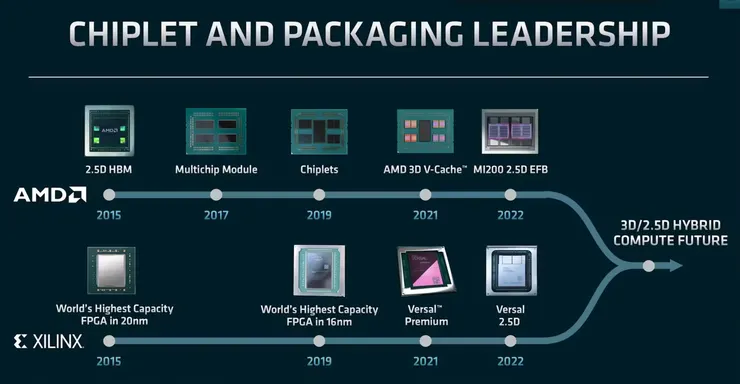

Xilinx 與 AMD 過去皆投入相似的 chiplet 與封裝技術,這讓雙方合併後的整合工作變得更為順利。

自 2010 年以來,半導體的微縮速度趨緩,市場也不再接受高成本卻效益有限的升級方式。於是,各大晶片廠開始轉向 chiplet 架構:

- AMD:Ryzen 7000 與 Genoa 系列導入 chiplet 設計,結合 3D 快取與多顆 CPU 晶粒

- Nvidia:H100 晶片面積已接近光罩極限,必須分割成多個 chiplet 才能製造

- Intel:Meteor Lake 採用 Foveros 3D 封裝,結合多顆異質晶粒

AMD 在 2020 年以 350 億美元併購 Xilinx,取得可重組架構(FPGA)技術。這筆收購不只是產品線擴張,更是為了進軍資料中心、5G、國防與高階工業等新市場,同時也擴充了其在 chiplet 設計上的彈性與整合能力。

製程極限下的突破:封裝技術成關鍵

晶片面積愈大,光罩(reticle)的物理限制就愈難突破。現階段單一晶片最大面積約為 858 mm²,一旦超過,就無法以單次光刻製作完成。High-NA EUV 雖然可以提升解析度,但對光罩、鏡頭與材料的要求也非常嚴苛,製造難度與成本大幅上升。

因此,將系統拆分為多個 chiplet,再透過高效封裝技術(如 TSV、Hybrid Bonding)組合,就成為應對製程瓶頸的解法。此外,不同 chiplet 可依功能選用不同製程節點(如 5nm CPU + 20nm I/O),也讓製造更具彈性與成本效率。大晶片不只製作難度高,良率也會隨面積增加而大幅下降。以面積超過 600 mm² 的晶片為例,即使使用最先進製程,整體良率往往僅有三成左右,導致成本暴增。

Chiplet 架構能將大晶片拆解成多個小晶片,單顆良率高,整體成本反而降低,是規模經濟在製程微縮受限時的新解法。這也讓 AMD 能有效利用 TSMC 的 7nm 製程生產高良率 chiplet,透過封裝整合出多核心架構,對抗 Intel 的單晶片設計。

模組化設計:IP 重用、製程混合、功能靈活

過去封裝只是為了把晶片裝起來,如今已變成整體設計的核心戰場

Chiplet 不只是封裝技術,更代表一種設計邏輯的轉變:

- 每一個 chiplet 都像是一個可重用的 IP 模組

- 可採用不同製程製作,再進行封裝整合

- 封裝過程可依功能需求調整排列組合

以 AMD 與 TSMC 合作為例,其 CPU 與快取晶粒分開製造,再以 copper-to-copper bonding 整合。Nvidia 則以大型 interposer 搭配 extra-long TSV,實現高頻寬互連。

此外,Xilinx 也曾提出 OpenHBI(High Bandwidth Interconnect)作為 chiplet 溝通標準之一。透過併購 Xilinx,AMD 不僅可整合該標準,還能打造完全由自家 IP 組成的 chiplet 系統,進一步掌握主導權。