icg

含有「icg」共 6 篇內容

全部內容

發佈日期由新至舊

付費限定

到了最後一個階段,

我們做了這麼多CG cell insertion後,

要怎麼知道到底是不是對Design有幫助的呢?

是否有個rule又或是量化的數據來解釋說CG的效果如何

在下面這篇paper中提到了幾種觀測CG cell efficiency的方法

J. Srinivas, M

前面文章曾經提到說,

除了我們在寫rtl當下直接撰寫加入的cg cell外,

實際上我們有些clk gating cell是靠tool自己幫忙插的,

[Verilog] 10分鐘由淺入深看懂 clock gating -2

那麼tool是怎麼判斷說哪邊要插gating cell的呢?

前面文章提到過clk gating check實際上就是在check gating cell的enable訊號

檢查enable的timing是否能滿足STA的check,

不過不知道各位有沒有發現到,

這條path看起來很單純呀而且我還用上了latch大法,

可能讓訊號走完1整個cycle

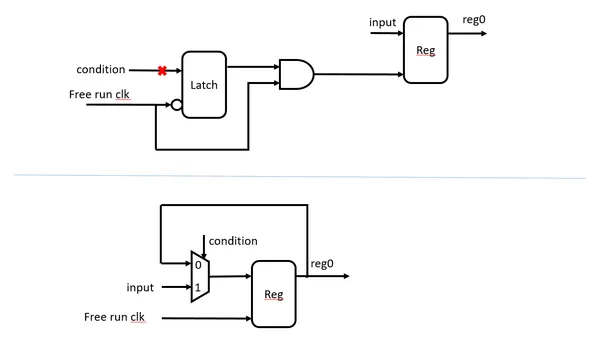

由於前篇提到說純的logic gate 的CG cell有些先天上的缺點在,

像是enable output 必須在指定的區間內才能trigger,

這也使的這條path上的timing變得更嚴苛,

因此就開發出了一個新的架構來解決上述的問題,

也就是大家常看到的latch based的cl

付費限定

介紹完了基本的概念後,

這邊來看個例子,

以and gated的CG來說 ,clk_enable 訊號由前一級的reg輸出(1) ,

經由Q輸出en後落在clk負緣的時候toggle (2),

下一個cycle的clk即會被鎖在0 (3)

對於or based的來說

clk_en

付費限定

先前文章中提提了幾種low power design常用的手法

[Verilog] 10分鐘看懂IC design的low power design - 1 (原創)

其中最廣為使用的招數就是clock gating

藉由停住當下沒在運作的module clk 及clk network 來達到