介紹完了基本的概念後,

這邊來看個例子,

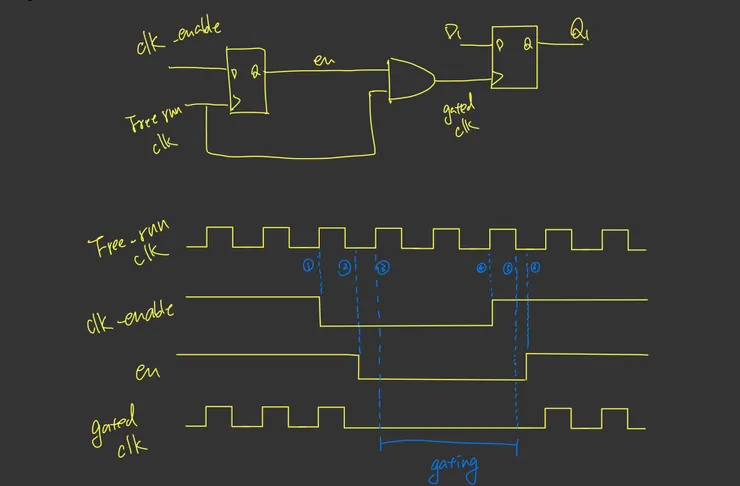

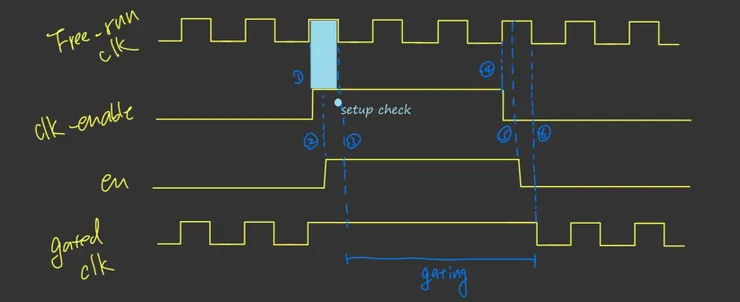

以and gate的CG來說 ,clk_enable 訊號由前一級的reg輸出(1) ,

經由Q輸出en後落在clk負緣的時候toggle (2),

下一個cycle的clk即會被鎖在0 (3)

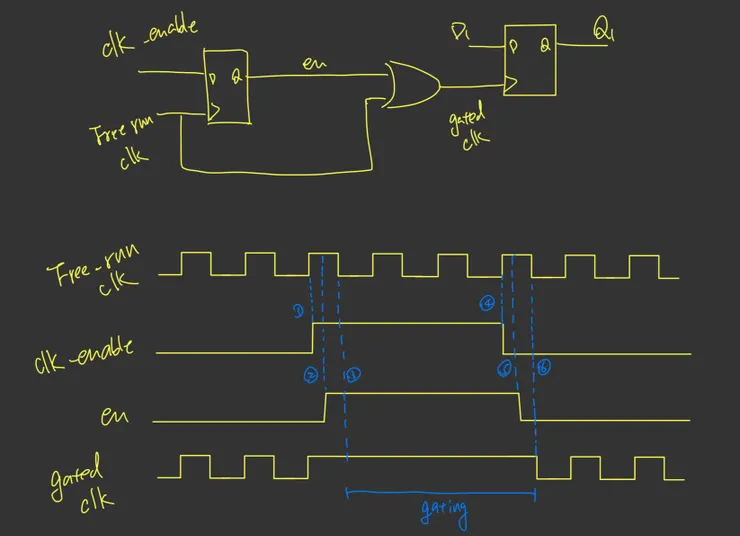

對於or based的來說

clk_enable由前一級Din輸入後 (1),

Q out於正緣輸出en給or gate (2),

output clk則會在下一次負緣到來時不會有任何動作(3),

上述的描述看起來都很直接沒什麼好質疑的,

不過不知道大家有沒有想過,

對於and based的enable要在負緣才能抵達and gated的input,

對於or based的enable則要在正緣抵達,不能是負緣,

or gate和and gate有著不同的enable setting的區間

但往往我們的enable是直接從reg output造出來的,

我們要怎麼控制他? 感覺就有夠難

實際上這邊可以裡用我們之前學到的一些技術來做到,

setup time 及 hold time,

setup time 指的是在 check point前最慢須穩定的時間,

hold time 指的是check point後訊號最少須維持多久的時間.

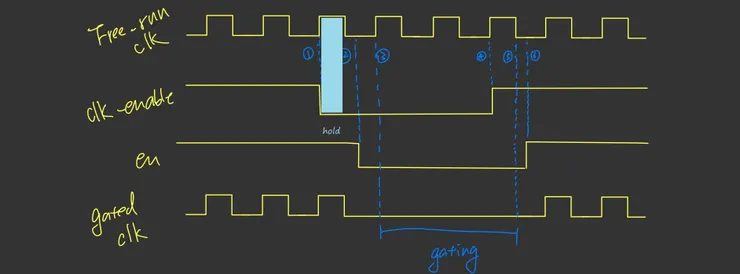

那麼我們先來看and gate based的

在clk_enable trigger後,必須在負緣的地方才能開始動,

所以我們只要把這顆reg的hold time直接強制拉到半T,

意旨clk trigger後訊號最少須維持半T的時間才能開始動,

tool就會為了meet STA不要發生hold time violation幫忙你用適合的方式卡住

那對於or gated based的來說

我們想做到的是enable被trigger後需要在正緣的階段就做完,

因此只要把setup check的位置從原本的下一個正緣往前拉半T,

就可以強制tool在半T的cycle把en訊號維持stable

不過design中的clk gating cell其實到處都是,

有些可能是自己塞得有些則是靠tool幫忙塞的,

我們基本上不太可能自己寫sdc把上述的constraint都設完,

要是漏了可能就直接白長一場,要怎麼辦?