由於前篇提到說純的logic gate 的CG cell有些先天上的缺點在,

像是enable output 必須在指定的區間內才能trigger,

這也使的這條path上的timing變得更嚴苛,

因此就開發出了一個新的架構來解決上述的問題,

也就是大家常看到的latch based的clock gating cell.

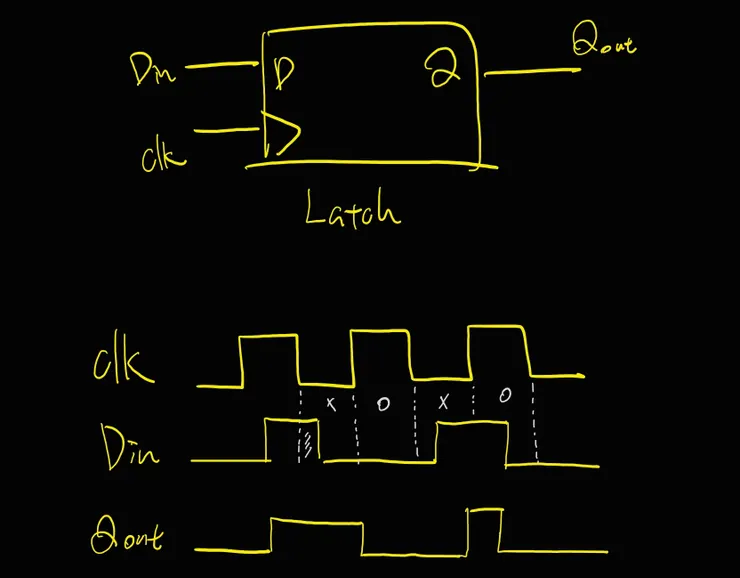

Latch和filpflop(register)不同的特性在於說,

Latch是level trigger的storage unit

filpflop則是edge trigger的storage unit

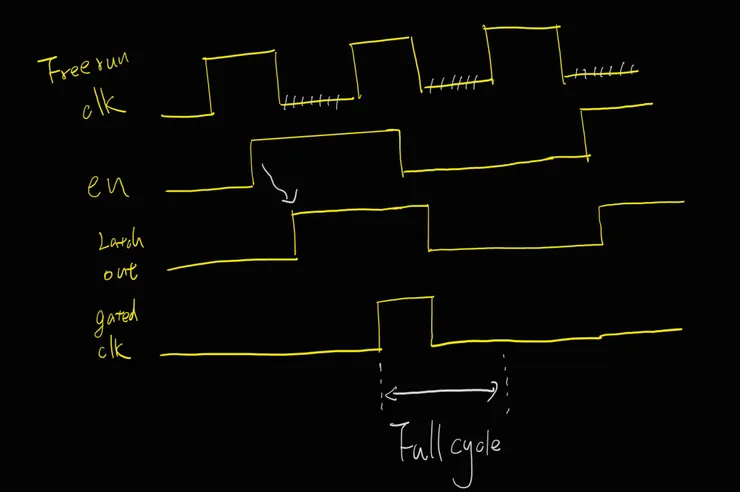

對於latch來說,clk的level為1則會去抓取Din的data

filpflop則是要在0->1的那個剎那才會做date update

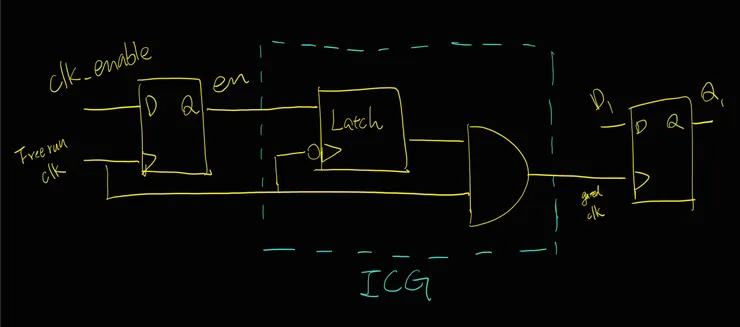

因此我們就利用了latch的這種特性,

只有在某半個cycle會去做data update,

另外半個則會鎖起來不會改變輸出,

這樣就可以解決前面提到的問題,

我本來必須靠限縮setup time或hold time來做到避免clk gating cell夾出不完整的cycle的問題,

這邊利用logic的特性,直接讓en沒辦法再不預期的時間內做update

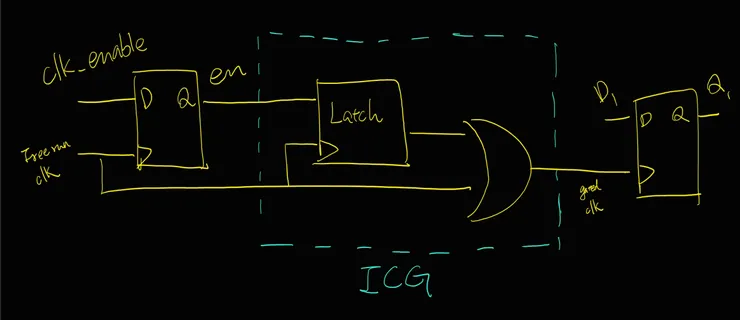

latch base 的CG cell一樣有兩種屬性,

和前篇提到的沒什麼不同,

兩個比較細節的差異主要就是餵給latch的clk是正緣還是負緣,

and gate的版本因為需要在clk負緣來時才能動作,因此latch的clk端需要加一個inveter給他,

or則是屬於正緣觸發,不必再額外多加電路

對這種變成了一個module味道的CG cell我們通稱它為ICG (Integrated Clock Gating)

在這個設計下,register的clk_enable只需要滿足最原先基本的setup time和hold time即可,

不足的部分直接靠latch的特性幫忙彌補,利用架構解來降低了timing收斂的難度,

在icg的情況下setup time及hold time不用再被額外多吃掉半T

看完這邊相信對於clock gating有一定程度的了解,

下一篇我們來做一些其他timing上的探討及統整個別的優缺

#clock gating check #CG #ICG #STA #low power #clock gating check #setup time #hold time #time borrowing #latch