clk gating系列文到了最後一個階段,

我們做了這麼多CG cell insertion後,

要怎麼知道到底是不是對Design有幫助的呢?

是否有個rule又或是量化的數據來解釋說CG的效果如何

在下面這篇paper中提到了幾種觀測CG cell efficiency的方法

J. Srinivas, M. Rao, S. Jairam, H. Udayakumar and J. Rao, "Clock gating effectiveness metrics: Applications to power optimization," 2009 10th International Symposium on Quality Electronic Design, San Jose, CA, USA, 2009, pp. 482-487, doi: 10.1109/ISQED.2009.4810342.

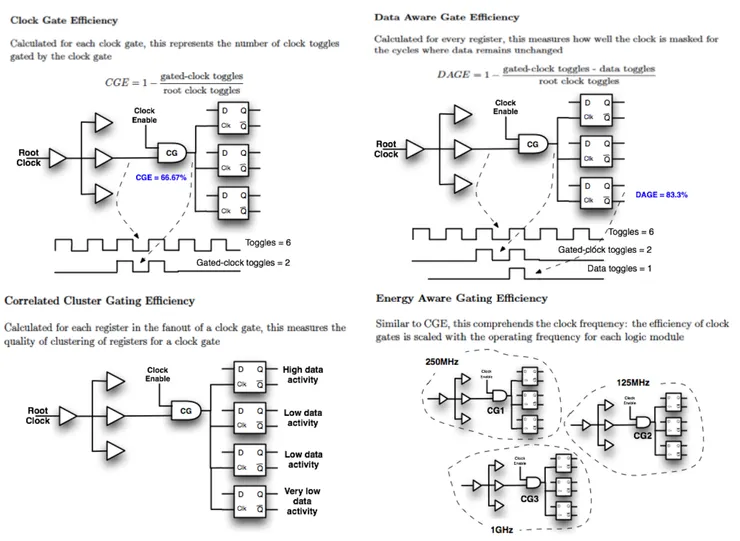

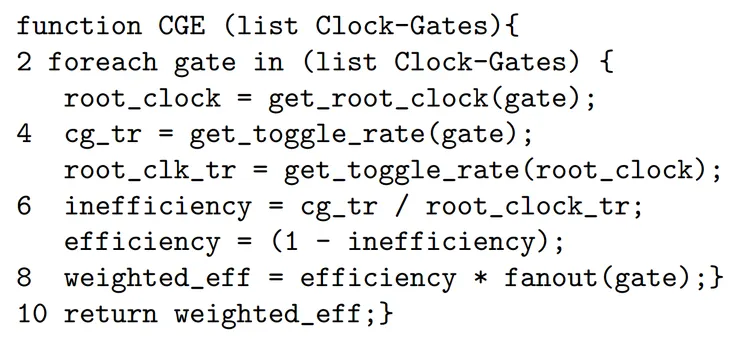

- Clock gating efficiency (CGE)

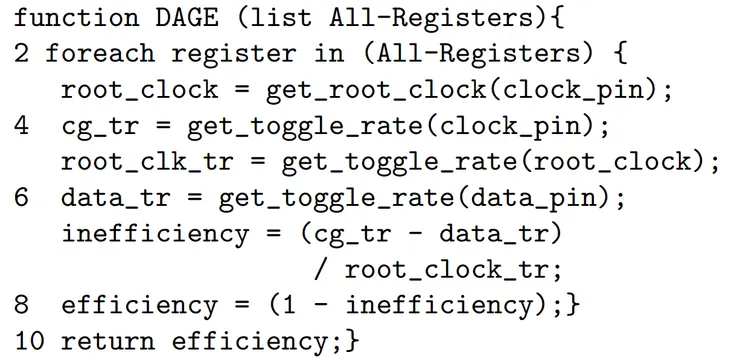

- Data-aware gating efficiency (DAGE)

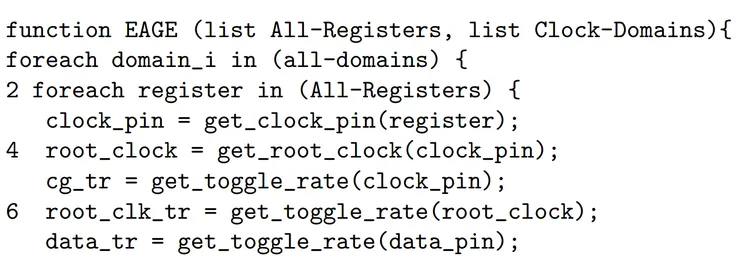

- Energy aware gating efficiency (EAGE)

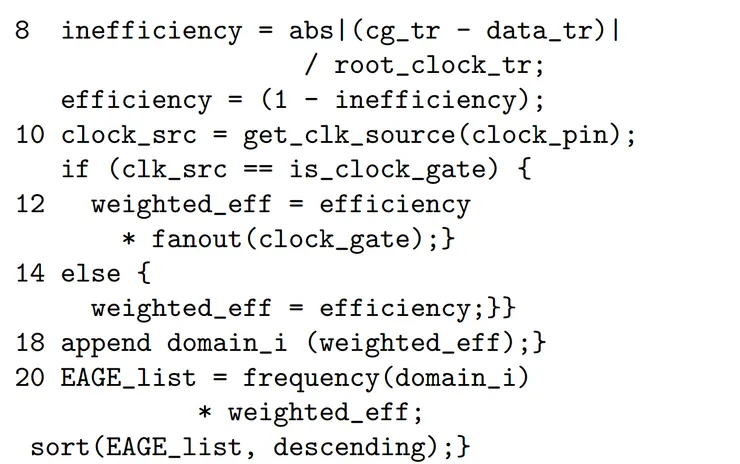

- Correlated cluster gating efficeny (CCGE)

CGE 著重於分析function運作中module被gating住的比例,

當gating ratio來的越高則得到的efficiency較好,省下較多的dynamic power

DAGE 則把觀察的對象改到了Data端,

藉由觀察每個gated clk的toggle是否都有對應的data的toggle,

如果clk toggle後data沒有翻轉的話則有機會再補充enable的條件來縮緊gating constraint

EAGE 考量了不同clk domain下的設計,

當系統中出現了多個clk domain時,freqency越高意味著power消耗越大

CG則可以依據clk domain做更細微的分割,

省下不同clk freq間reg clk運作次數造成的power消耗

CCGE專注於分析於同一個CG下的fanout group,

對於不同的module或function使用同一個CG的clk下,

可能有些module處於heavy load 有些module則處於light load,

此時如果都共用同一支enable出來的clk,

enable區間會被heavy load的那方主宰,

讓處於light load的module無法關閉clk導致多餘的power消耗

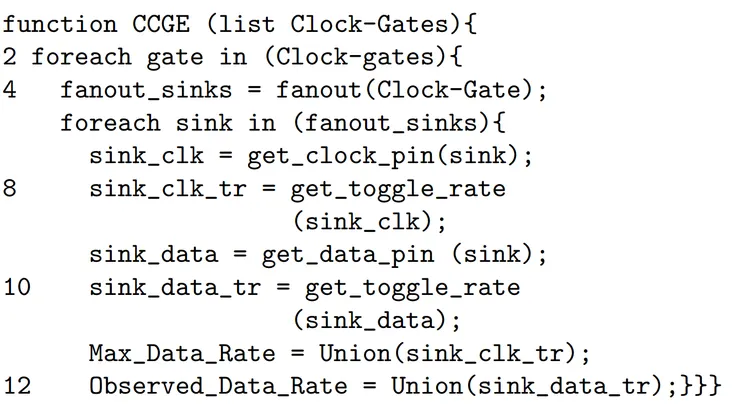

除了上述的指標分析外,

synthesis 完成後也可以藉由 report clock_gating -summary 來吐出相關的information,

report中會提供cg相關的資訊,

從table中可以觀察total filpflop number vs ungated的filpflop,

RC clock gating vs non-RC clock gating 數量,

判斷相關的數據是否合理來debug相關的問題

最後來想一想,

從上面的table中可以看到並不是所有的filpflop 都被clk gating control,

形成的原因可能是甚麼呢?

在report中可以看到total ungated filpflop有8顆,