大家早安。當我們今天打開新聞,看到 Nvidia H100 或 B100 搶手缺貨時,最常出現的關鍵詞就是高頻寬記憶體(HBM, High Bandwidth Memory)。這不只是一顆記憶體晶片,而是一段延續八十年的故事。從 1945 年馮紐曼架構的誕生,到 1970 年代 DRAM 的崛起,再到 2025 年 AI 伺服器上環繞 GPU 的 HBM 堆疊,這條演進脈絡背後隱藏著同一個問題:處理器與記憶體之間的速度落差。

馮紐曼架構與瓶頸的起點

First Draft of a Report on the EDVAC 電腦科學最原始的文件,完整描述了儲存程式架構,被視為後世電腦的藍圖。

然而,它也留下了一個結構性的限制:處理器再快,依然必須等待記憶體提供資料。這就是後來被稱為馮紐曼瓶頸 Von Neumann bottleneck 的問題。當處理器速度成長快於記憶體頻寬時,效能便被拖累。

1978 年,圖靈獎得主 John Backus 在演講〈Can Programming Be Liberated from the von Neumann Style?〉中,甚至批評這種序列式思維讓軟硬體都受限。到了 1995 年,Wulf 與 McKee 在論文《Hitting the Memory Wall》進一步提出記憶體牆的比喻,形容 CPU/GPU 雖然持續加速,但最終會撞上記憶體的天花板。

這些討論在當年看似理論,卻在今日 AI 晶片的設計中完全成真。

DRAM 的誕生與成就

1970 年代,DRAM(Dynamic Random Access Memory)開始大規模量產,成為電腦的核心記憶體。它的原理簡單:用電容存放一個位元,透過刷新保持資料。這種設計雖然需要持續供電,但在成本與面積效率上非常出色。

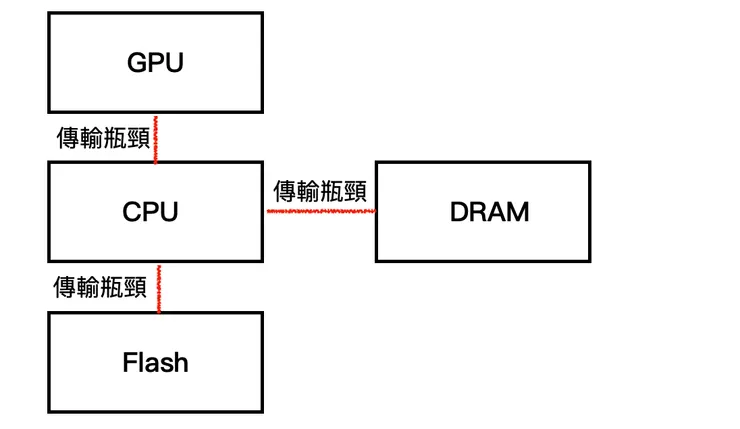

DRAM 的容量擴張速度驚人,從最初的幾 KB 到今日的數十 GB,支撐了 PC、伺服器與手機的演進。對大多數運算來說,DRAM 依然是最佳選擇。但隨著處理器性能爆炸性成長,DRAM 的存取速度與頻寬卻顯得捉襟見肘。這就是所謂的記憶體瓶頸。

業界的第一個回應是快取 (Cache),在處理器與 DRAM 之間設置更小更快的 SRAM 緩衝層,以減輕延遲。這種設計延續至今,成為 CPU 與 GPU 的標配。但當進入 AI 與高效能運算時代,快取再多也不足以承受數萬個運算核心同時存取的壓力。

HBM 的誕生:立體的解法

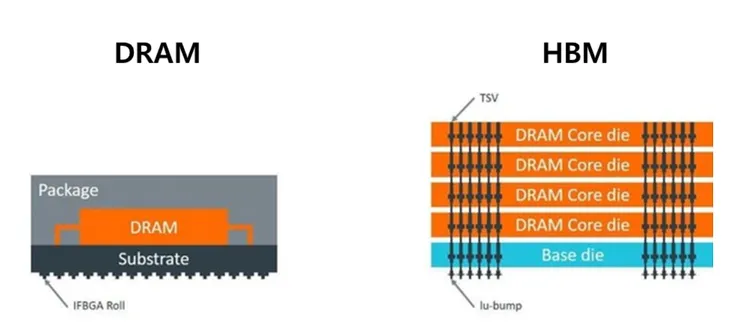

HBM 多層 DRAM 晶片透過 TSV 垂直連結。

2015 年,AMD 與 SK hynix 首度推出 HBM,應用在 Radeon Fury X GPU。這是一種根本性的改變,突破點不在電路單元,而在封裝方式。

HBM 使用 TSV(矽穿孔)技術,將多層 DRAM 晶片垂直堆疊,並透過中介層與 GPU 或 CPU 並排。這樣的設計大幅縮短資料傳輸距離,提高頻寬並降低功耗。

如果說 DDR 是在水平公路上不斷加寬車道,HBM 則是直接在處理器旁邊蓋一座立體交流道,讓資料能垂直流動。

很多人會問:HBM 的協定是不是 DDR5?答案是否定的。

HBM 雖然與 DDR 系列一樣屬於 DRAM 技術,但它是JEDEC 另行定義的專用標準,協定完全不同。

- DDR4、DDR5 是為 DIMM 模組設計,透過主機板記憶體槽與 CPU 控制器連線。

- HBM 則是 堆疊式記憶體,直接透過 TSV 與中介層連到處理器。它走的是寬匯流排、低頻時脈、多通道的傳輸協定。

換句話說,HBM 並不遵循 DDR5 的協定,而是有自己的一套 HBM1/HBM2/HBM3 標準。例如 HBM3 每顆晶片最多 16 個通道,每通道 64bit,總位寬可達上千 bit,這就是它能提供 TB/s 級頻寬的原因。

這也是為什麼 HBM 必須緊密貼合在 GPU 或 CPU 旁邊,無法像 DDR5 那樣做成插槽模組。

- HBM1(2015):首度商用,雖然成本高昂,但展示了立體堆疊的潛力。

- HBM2(2016 起):應用於 Nvidia Tesla P100、AMD Vega,頻寬翻倍,容量提升。

- HBM2E(2019):進一步提高傳輸速率,支撐更多 HPC 與雲端 AI 任務。

- HBM3(2022):成為 Nvidia H100 的標準配置,每秒頻寬達數 TB,正式進入 AI 大規模訓練的核心。

- HBM3E(2024)與 HBM4(2025 規劃中):容量與層數持續提升,並與台積電 CoWoS、InFO、Intel Foveros 等先進封裝技術緊密結合。

每一代 HBM 都不是單純的製程縮小,而是透過系統級設計推進。

H100 與 HBM 的配置

Nvidia H100 是最能體現 HBM 價值的例子。其 SXM5 版本(一種伺服器專用的 GPU 模組規格,能承受超過 700W 功耗)在封裝上預留六顆 HBM,一般機型啟用五顆(80GB HBM3),部分 NVL 版本(Nvidia Large Memory,專為大型語言模型訓練設計)則六顆全開,容量更高。

H100 的另一種 PCIe 版本(通用的高速擴充插槽介面,常見於 PC 與伺服器)雖然外型像顯示卡,但因功耗上限較低,效能不及 SXM5 模組。

這些 GPU 的運算核心被稱為 CUDA 核心(Compute Unified Device Architecture,是 Nvidia 的平行運算平台),讓 GPU 不只跑圖形,也能加速 AI 與科學計算。CUDA 是軟體平台的名字,但也成為描述 GPU 運算單元數量的代稱。

這些差異看似細節,卻決定了伺服器的吞吐能力。正因如此,2023–2025 年間,HBM 產能緊缺成為 AI 晶片供應鏈的最大瓶頸。

全球主要供應商只有 SK hynix、三星、Micron 三家。SK hynix 在 2023–2025 年市佔率領先,三星力圖追趕,Micron 則試圖透過 HBM3E 打破韓廠壟斷。這些動態甚至成為資本市場的焦點。

HBM 與 DRAM 的分歧

雖然名稱相似,HBM 與 DRAM 的應用領域卻完全不同。

- DRAM:容量大、成本低,是 PC 與雲端的基礎。

- HBM:頻寬極高、功耗低,但成本昂貴,專屬於 AI 訓練、超算與高端繪圖。

這就像日常道路與 F1 賽道的差異。大部分人只需要能通行的道路,只有極端場景才需要極速賽道。而 HBM,正是 AI 的專屬賽道燃料。