特別感謝國票投顧於 2024/02/16 舉辦的線上論壇 《晶片指紋-PUF》,讓我終於對這個產業的理解往前推進了一大步,也非常感謝熵碼科技詳細的 Youtube 課程。

以下研究僅為分享,不具投資建議,希望能以最淺顯易懂的方式幫助大家理解這個市場。

一、結論

- 隨著 AIoT 市場逐漸成熟,資安意識、邊緣運算需求提升,整體加密晶片技術的市場成長性可期。

- 台灣加密晶片技術的代表廠商為力旺 (3529),除了公司本身技術已非常成熟外,利用 QTPUF 的方式增強晶片的安全性,目前市場上無競爭對手,具備產業獨特性。

二、加密晶片技術介紹

傳統上,訊息安全僅強調傳輸通道的安全性,駭客可能會透過竊聽、竄改等方式干擾訊息的傳遞,不過此種方式透過密碼學演算法、通訊協定等方法即可防範大部分的攻擊。

隨著科技進步,駭客的攻擊形式也越來越多元,收發訊息的硬體也是駭客主要攻擊的對象,常見的駭客攻擊形式:

- Software attacks:透過軟體的方式攻擊,例如惡意軟體、勒索軟體等

- Side-channel attacks:利用硬體散發出來的訊息痕跡,例如功率消耗、電磁洩漏、聲音等,來分析數據的攻擊方式

- Reverse engineering:根據惡意程式分析、漏洞挖掘或軟體破解的方式,逆向得出相似的產品,為一種技術仿造的過程,透過這種方式直接更改晶片製程進行攻擊

- Invasive attacks:可能會透過 laser injection 的方式破解晶片的設計,進而癱瘓整個裝置系統

有句話說 "Security is only as strong as the weakest link",因此假設有一個環節的安全性被攻破,那整個系統的安全其實就不存在了。

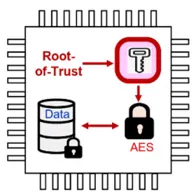

該怎麼防範呢?最好的方式是提升晶片層級的安全性,確保唯一源頭 (Root of Trust)。

- 加入信任鏈結構 (chain of trust)

- Data 透過 AES 技術加密保存,確保 Data 是 confidencial

- AES 只可透過唯一的 Key 來啟動,也就是符合 Root of Trust 的原則,i.e. 安全晶片或 IP block

- 因此,Key 需要具備不可預測性,且符合物理上安全的特性

資料來源:PUFacademy

Key 目前最好的解決方案:PUF

1. PUF 是什麼?

PUF 可以想像成晶片的指紋,它是源自於 mosfet 本身的細微變異,而這些變異已無法再透過更先進的製程改善,具備隨機性且符合最大亂數 (entropy) 原則。

PUF 是存在於每個晶片上的變異,最簡單的生成方式是透過通電來讓密碼浮現,斷電後密碼即消失,因此無須額外的儲存元件,可降低生產成本。

PUF = 密碼生成 + 密碼儲存

好的 PUF 需要具備的特點:

- 獨特性:每個晶片都有自己的 PUF

- 可靠性:不同的外在條件 (e.g. 時間點、溫度、電壓) 均會產生相同的密碼

- 由物理特性產生

- 不可複製與不可竄改性

2. 目前比較常見的 PUF 生成形式:SRAM PUF vs QT PUF

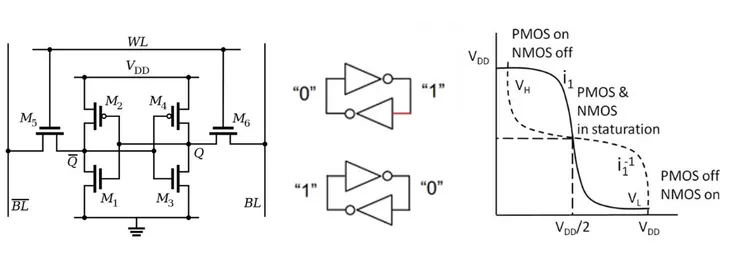

a. SRAM PUF

簡單來說,當一個 mosfet 通電後,理論上電流方向從右邊流到左邊 (假設為 0),或由左邊流到右邊 (假設為 1) 的機率應該是 50%、50%,但基於一些元件的本身性質和電流的不穩定性等,這會導致整個晶片出現 0 和 1 的機率不是 50%、50%,再加上這個方式可能會產生一些 bit error rate,導致有些元件上的電流每次通電後產生的方向不同,無論是短期或長期造成的破壞,都有可能讓最後生成的密碼和原始的不同,因為這些不穩定和非隨機性,SRAM PUF 並不是一個很好的解決方案。

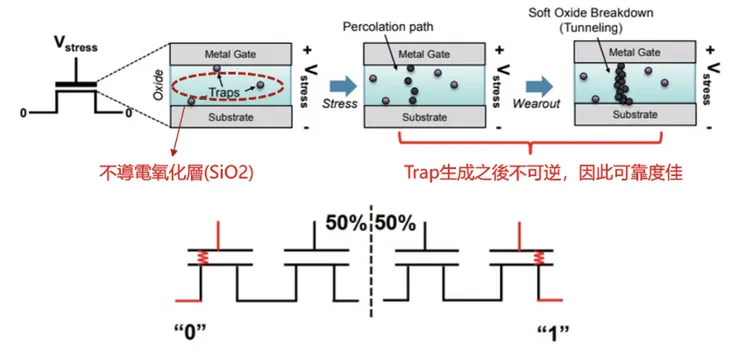

b. Quantum Tunneling PUF (QT PUF)

資料來源:PUFacademy、國票投顧

在元件中間有一層不導電氧化層,加壓後會形成永久的缺陷,又稱為 traps,當加壓到一個程度後,traps 就會形成一個通道,讓電子可以通過這個氧化層到另一端。

兩個元件擺在一起,在上面進行加壓後,會有 50%、50% 的機率電子由左邊或右邊流出 (根據方向假設 0 和 1),這個破壞從外觀上是看不出來的,因為元件本身非常小。

QT PUF 具備很好的隨機性和可靠性,因為氧化層的破壞是永久的,每一次加壓後並不會造成密碼的改變,換句話說,這些電流的方向是存在於晶片本身的特性,如同晶片的指紋一樣,每一個晶片都會有獨一無二的密碼。

資料來源:國票投顧、自行整理

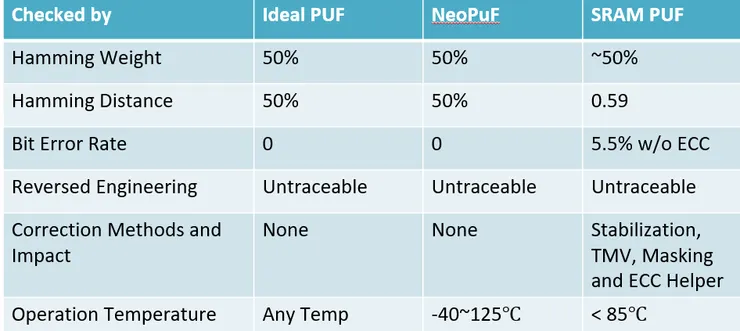

Hamming 係數就是上述提到的,出現 0 和 1 的機率,50% 即為最完美的比例,被駭客用暴力破解的機率最低。

NeoPUF 為力旺根據 QT PUF 原理註冊的商標,可以看到除了完美的 Hamming 係數外,NeoPUF 最適的運作溫度介於 -40~125℃,剛好符合汽車電子零件的需求,因此未來有機會被廣泛使用。

三、台灣加密晶片技術的代表廠商-力旺 (3529)

力旺是嵌入式非揮發性記憶體 (Embedded NVM) 技術開發與矽智財 (IP) 授權的廠商,產品涵蓋 OTP / MTP 與快閃記憶體。在 2019 年跨入晶片安全領域,導入反熔絲可一次編成記憶體 (anti-fuse OTP) 與物理不可複製功能 (PUF) 技術。

力旺的記憶體 IP 僅需將晶片所需的記憶體位置空出,並嵌入晶片上的位置即可提升產品效能。

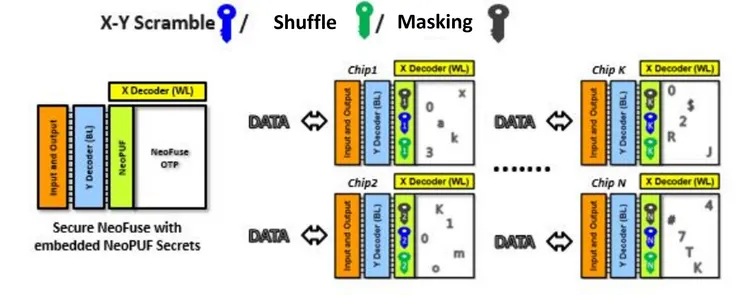

每一個 NeoFuse OTP 的技術,都是利用天生的 NeoPUF 進行加密,基於 QT PUF 原理,具備安全性高、功耗低且設計簡單的特性。

資料來源:PUFacademy、電子工程專輯

因為這些 NeoPUF 是獨一無二的密碼,因此我們需要透過記憶體本身的特性和一些方式來保護這些密碼不易受到破解。

所有需要存儲的晶片都可以透過 PUF 的技術加密。

四、市場成長性

資訊安全市場

- IEK 預測 2026 年台灣資安產業產值將達千億台幣以上,每年產值雙位數成長。

- 根據 The Insight Partners 預估,全球資訊安全市場份額將在 2030 年達到 6,606.7 億美元,2022 年至2030 年 CAGR +15.9%。

隨著 AIoT 市場逐漸成熟,人們對於資安的重視程度增加,加密晶片的應用也會越來越廣泛。

邊緣運算市場

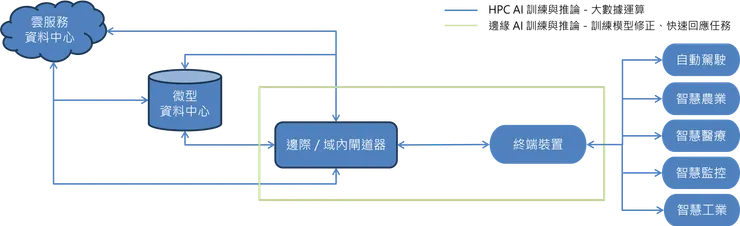

資料來源:MIC、自行整理

- 全球邊緣運算市場規模根據 MarketsandMarkets 預估,將從 2023 年的 536 億美元成長至 2028 年的 1,113 億美元,CAGR +15.7%,主因是需求將從 AR / VR 拓展至智慧醫療保健、智慧工業、智慧監控等產業的 AIoT 設備上。

過去傳輸資料時會將資料從終端裝置傳回雲端,但資料量龐大會造成數據分析的延遲,而連網也會有安全性的問題,因此,邊緣運算直接將運算工作放在靠近終端裝置或終端裝置上,無須仰賴雲端,也可以不連網直接進行 AI 推論,透過分散式和本地執行的方式進行數據處理和分析,降低延遲性,可大幅增強安全性,確保資料機密。

五、附錄

一、物理特性為何安全

假設有一個方程式,若將 a 丟入一個 function 後得到 b,事實上我們可以利用公式計算出答案,或是利用 Machine learning 等的方式找到這個 function,進而回推 a。

這個方法在科學上其實是不安全的。

a → f(x) → b那什麼方式才是安全的呢?

骰子的隨機性。

骰子在擲出每個數字的機率是一樣的,無法預測下一次會是哪一個數字,那我們就稱這個特性為物理上的安全性,由物理現象產生的,具備隨機性,才能達到真正意義上的亂數。

二、PUF 的必要性

隨著數據中心的安全性需求提升,AMD、Google、Miscrosoft 和 Nvidia 合作開發 Caliptra 計畫,規範硬體信任根 (Hardware Root of Trust, HRoT) 的必備組成標準。

Caliptra 是將安全機制整合到晶片中的開源規範,作為開放運算計畫 (OCP) 的參考設計。主要目標是為 HRoT 建立開源的標準,用來內嵌 CPUs、GPUs、SoCs、ASICs、網路晶片、SSDs 和其他設備中的硬件加密,規範 TRNG、OTP、PUF 成為 HRoT 標準的必備組成,但因為 HRoT 屬於 Hard IP,無法透過開源取得,因此需要取得授權。

雖然 Caliptra 仍處於非常早期的階段,預估未來所有數據中心將更廣泛採用硬體及安全方案,這也意味 PUF 相關技術將有更廣大的市場。

六、參考資料

- 在AIoT时代,如何用指纹芯片技术来保护我们的芯片和数据?

- 淺談信任根(RoT)解決方案—NeoPUF

- 量子穿隧PUF信任根: PUFrt

- PUFacademy

- 國票投顧論壇《晶片指紋-PUF》