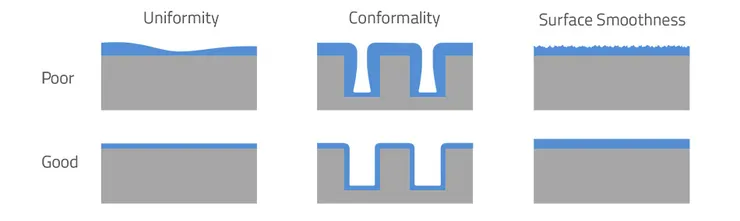

左邊的 Uniformity(均勻性),指的是薄膜在整片晶圓上的厚度是否一致。均勻性差,代表有些區域太厚、有些太薄,會直接造成電阻不一致與良率下降;好的沉積,必須讓整片晶圓像鋪平的地毯一樣穩定。 中間的 Conformality(覆蓋性),描述薄膜能否完整包覆立體結構的側壁與底部。當結構越深、越窄,覆蓋性不足就會導致空洞或斷層,這也是先進節點最容易出問題的地方。 右邊的 Surface Smoothness(表面平整度),則影響後續製程與可靠度。表面越平滑,界面缺陷越少,電性與壽命也越穩定。 不論採用哪一種沉積方法,所有技術演進的終極目標,其實只有一件事:在複雜結構中,同時做到均勻、完整、且可量產的高品質薄膜。

半導體製程裡,沉積(deposition)聽起來像把材料鋪上去這麼簡單,但實際上它決定了良率、功耗、甚至節點能不能量產。要把這件事看懂,先把三個名詞釐清:PVD、CVD、ALD。它們不是同義詞,而是對應不同結構難度與風險層級的三種工具。

- PVD 是把材料打上去,速度快、金屬純度高。

- CVD 是讓材料自己長上去,量產穩定、覆蓋性好。

- ALD 則是一層一層精準堆,原子級控制、但慢且貴。

CVD(Chemical Vapor Deposition)靠氣態前驅物在表面發生化學反應,薄膜是「長出來」的。覆蓋性與均勻性優於 PVD,長期是量產線的主力,從介電層到各類功能薄膜都靠它撐場。當結構再往三維推進,CVD 會碰到精度極限,這時就需要更細的工具。

ALD(Atomic Layer Deposition)把精準拉到極致。自限制反應讓每一次循環只生成一層原子厚度,幾乎不受結構形狀影響。FinFET 後段、GAA、高深寬比結構都離不開 ALD。代價是速度慢、成本高,所以它只用在不用不行的地方。

(延伸閱讀:半導體製程系列 6/ 8 | 沉積與磊晶:打造晶片的奈米塗層)

Applied Materials(AMAT)

AMAT 橫跨 PVD、CVD、ALD,但它賣的不是單一技術,而是整段流程的風險管理。多腔體平台、連續沉積、界面與應力的一體化控制,讓 fabs 用系統下決策。在先進邏輯與先進封裝裡,AMAT 常成為主供應商,原因是整體不確定性最低。

Tokyo Electron(TEL)

TEL 的工程哲學是把單一製程步驟做到極度穩定。它在 CVD 與 ALD 的均勻性、重複性與長時間量產可靠度上口碑極深,特別受記憶體與大量量產線信任。策略上,TEL 會挑最影響良率的關鍵層切入。

ASM International

ASM 是 ALD 的純血玩家。原子級控制、高深寬比與界面品質是它的主場。當製程對變異性零容忍時,ASM 常是標準答案。ALD 的滲透率提升,幾乎等同於 ASM 的結構性利多。

Lam Research

Lam 的核心在蝕刻與清洗。它不直接和沉積搶位置,卻決定沉積能不能成功。把結構刻乾淨、表面準備好,後面的 PVD、CVD、ALD 才能發揮理論值。三維化越深,Lam 的戰略地位越高。

先進邏輯節點中,PVD 的戰略重心逐步移向 BEOL 與先進封裝

BEOL(Back End of Line)指的是電晶體完成之後的所有金屬互連工程,真正把前段做好的元件,用一層又一層金屬線接起來,讓晶片可以實際運作;而先進封裝,本質上就是 BEOL 的延伸,將互連一路拉出晶片本體,進入晶圓級與封裝層級。

這也正是 PVD 戰略重心逐步移向 BEOL 的原因。PVD 最擅長的其實不是處理又深又窄的立體結構,而是高品質、高純度的金屬薄膜。在早期節點,FEOL(Front End of Line,指的是半導體製程中「把電晶體本體做出來」的那一段工程)。結構相對平面,PVD 還能勝任,但從 FinFET 走向 GAA,結構深寬比急遽拉高,原子直線飛行的物理特性開始吃虧,洞底與側壁覆蓋性不足,使得 FEOL 關鍵層逐步由 CVD 與 ALD 接手。然而這並不代表 PVD 退場,而是舞台轉移。

因為在 BEOL,真正關鍵的是金屬純度、低電阻、應力控制、大面積均勻性與高吞吐量,這些全部都是 PVD 的強項,從金屬 seed layer、barrier 與 liner、厚金屬層,到封裝用 RDL,以及 HBM 與先進封裝的金屬互連,PVD 幾乎無可取代。

換句話說,FEOL 在意的是「怎麼鍍得進去」,BEOL 在意的是「怎麼鍍得好、鍍得快」。而當 CoWoS、InFO、Foveros 等先進封裝架構成為主流,金屬層更厚、面積更大、成本與產能壓力同步放大,你不會選擇用 ALD 慢慢堆原子,而是需要高速、穩定、可擴產的金屬沉積,這正是 PVD 的甜蜜點。

因此所謂「PVD 的戰略重心移向 BEOL 與先進封裝」,真正的意思並不是重要性下降,而是從電晶體本體,轉向決定晶片如何被連接、被封裝、被放大系統效能的核心位置,也解釋了為何 Applied Materials 持續加碼封裝 PVD,市場也開始重新評價先進封裝不是次要製程。