🟩 AI GPU「一定要」用HBM(物理原因)

這不是單純工程選擇,而是 AI 計算物理極限 的結果。

一句話:AI ≠ compute problem,而是 memory movement problem

下面從物理層 → 架構層 → AI scaling 層,完整講清楚。

⭐ 一、AI 計算本質:資料搬移主導

在 LLM / Transformer 中:

Compute FLOPs << Memory traffic

原因:

- 權重矩陣巨大

- activation 巨大

- KV cache 巨大

- attention streaming

👉 GPU 大部分時間在 等資料

這就是 memory wall

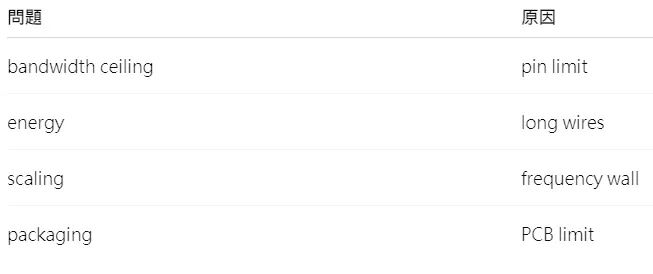

⭐ 二、Memory wall 的物理來源

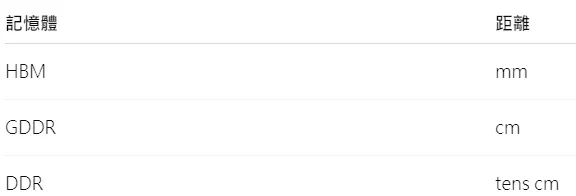

🔷 1️⃣ 電子傳輸距離

功耗近似:

Energy ∝ capacitance × distance👉 距離越遠 → 功耗越高

比較

👉 HBM 最短

🔷 2️⃣ Pin density 限制

傳統 DRAM:

- PCB trace

- package edge pins

👉 IO pin 數量受封裝限制

結果

👉 bandwidth ceiling

🔷 3️⃣ Frequency scaling 不可行

GDDR 想提高 bandwidth:

bandwidth = pins × frequency

但:

- 高頻 → signal integrity

- jitter

- power

- EM loss

👉 GHz scaling 成本極高

⭐ 三、HBM 的物理解法

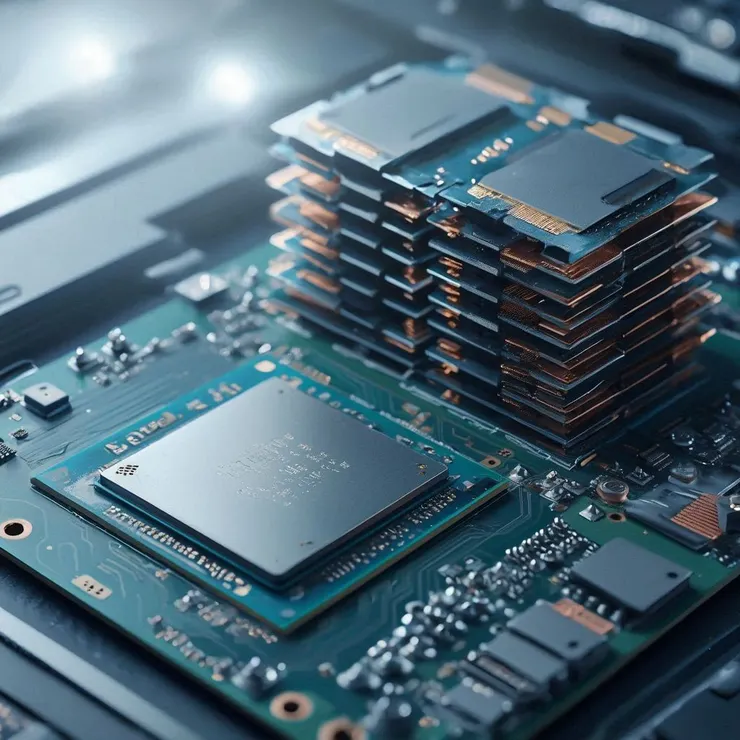

🔷 HBM = 3D + 2.5D integration

HBM 使用:

- TSV(Through Silicon Via)

- silicon interposer

- 3D stack

👉 本質 = memory proximity engineering

🔷 1️⃣ 超寬 IO(核心)

HBM:

- 1024 bit / stack

- 多 stack

👉 aggregate bus width = tens of thousands bit

GDDR:

- 32 bit channel

👉 HBM 用寬度,不用頻率

🔷 2️⃣ mm 級距離

HBM:

- GPU die 旁邊

- interposer

👉 RC delay ↓

👉 energy ↓

🔷 3️⃣ 並行 memory banking

HBM stack:

- 多 die

- 多 bank

👉 massive parallel memory

適合:

- matrix streaming

- tensor access

⭐ 四、AI 為何比 graphics 更依賴 HBM

🔷 Graphics

- cache reuse

- locality

- pipeline reuse

👉 bandwidth 壓力較低

🔷 AI

- weight streaming

- activation streaming

- KV cache

👉 near worst-case memory pattern

⭐ 五、Scaling law 使 HBM 成為必然

AI scaling:

model size ↑

context ↑

batch ↑

👉 memory traffic ≈ O(N)

Compute scaling:

👉 O(N log N)

👉 memory 變 bottleneck

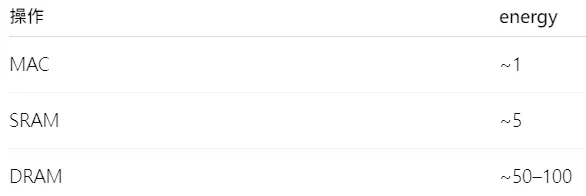

⭐ 六、Energy economics(最深原因)

移動 32bit:

👉 memory access ≫ compute

HBM 目標:

👉 降低 memory energy

⭐ 七、為何 GDDR 不行

👉 GDDR 是 PCB memory

👉 HBM 是 package memory

⭐ 八、最直觀理解

🔷 GDDR

👉 memory 在城市外

👉 要開高速公路

🔷 HBM

👉 memory 在 CPU 旁

👉 走小路

👉 latency ↓

👉 energy ↓

👉 bandwidth ↑

⭐ 九、一句話物理結論

AI GPU 必須 HBM,因為 memory movement energy dominates compute energy,而 HBM 是唯一能降低 movement energy 的封裝技術

⭐ 十、延伸前沿(非常重要)

HBM 之後:

- HBM4

- optical memory link

- wafer-scale memory

- memory fabric

👉 AI computing → memory-centric computing