在這兩篇曾經提過PCB Layout對於晶片溫度有著不小的影響:

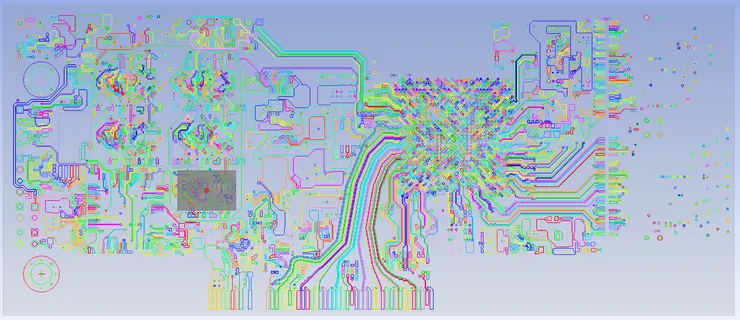

這篇透過3種狀況來比較其表現,分別是: 載入真實線路,等效熱傳導係數,以及一整塊FR-4,分別對應Rjb從大到小,讓大家用模擬感受一下其差異。模型很簡單,就是一張Add-on card上面打一顆SDRAM。

根據Datasheet,SDRAM Rjb=17.4C/W, Rjc=5.9C/W,Power設定為1W。

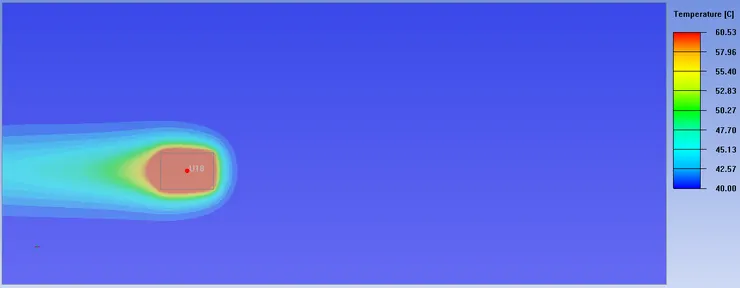

而PCB是一張1.6mm的八層板,搭配上V=1.5m/s由右往左吹的水平風,結果到底是人體無感,還是茲事體大呢?

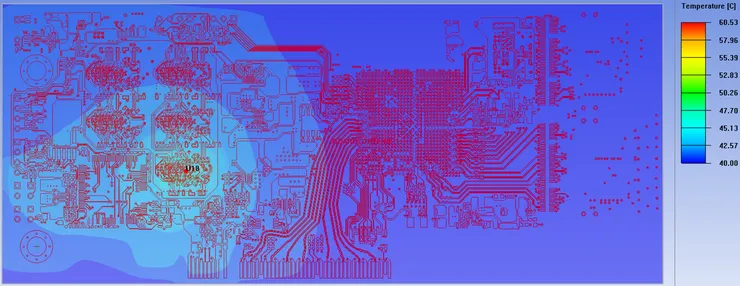

Case1: PCB with imported layout- Tj=61.23C

Case2: PCB with effective thermal conductivity– Tj=74.91C

Case3: PCB with all FR4– Tj=98.63

從模擬結果可以發現Layout影響相當大,從高到低可以相差有30C,的確大部分的熱是從透過Via從BOT側離開或是透過TOP的銅擴散出去協助散熱。

在CASE1中可以很明顯地看到熱沿著線路以及內層Plane的方向走。

在CASE2中稍微可以看到擴散的效果但是已經受到了很大程度的截斷,同時,無法表現出通往背面的VIA效果。

在CASE3幾乎就是限制了只能從IC表層離開。

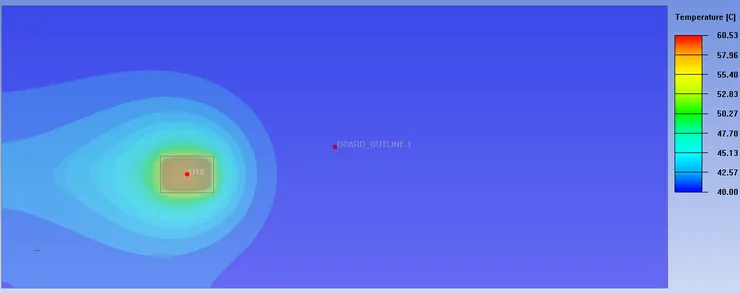

後續又做了一組CASE1與CASE2上面加上Heatsink的對照,結果是

Case1: Tj=58.64C

Case2: Tj=61.82C

說明從BOT散出的熱其實是不能忽略的,而效果跟一個HS差不多

如果將發熱量提高到5W

Case1: Tj=134.2C

Case2: Tj=187.6C

在瓦數提高的狀況下更為明顯,除了在設計HS降低Rca以外,調整Layout讓熱能順利走到背面完全是必要的。

最後是使用Icepak模擬IC Package的小注意事項:

1. 可以使用Block中的network來使用2R model模擬熱阻效應,但是

熱阻模型下的內部解空間是架空的,IC內部是沒有網格且沒有資料。

2. 如果要模擬Heatsink的效應,可以使用熱阻block,或是廠商提供的CCM模型,上面搭配HS模型處理,至於等效block現在認為有點雞肋。

3. 曾經考慮過用均質發熱block搭配等效k值,但是後來覺得,IC發熱模式由中心晶片產熱,經由基板導線架,走到封裝外殼,其實用2R熱阻模型更適合,而非整個IC都在發熱。再者是做fitting的時候,用2R來控制,直觀且線性,用k值調整反而難表現上下散熱路線差距,同時既然兩者除去Tj外IC內部溫度都沒有意義,那其實沒有必要下這番功夫。