超級成長:小晶片市場

隨著技術的發展,半導體製程技術正逼近其物理極限,小晶片(Chiplet)技術被半導體業界視為超越摩爾定律物理極限的關鍵。

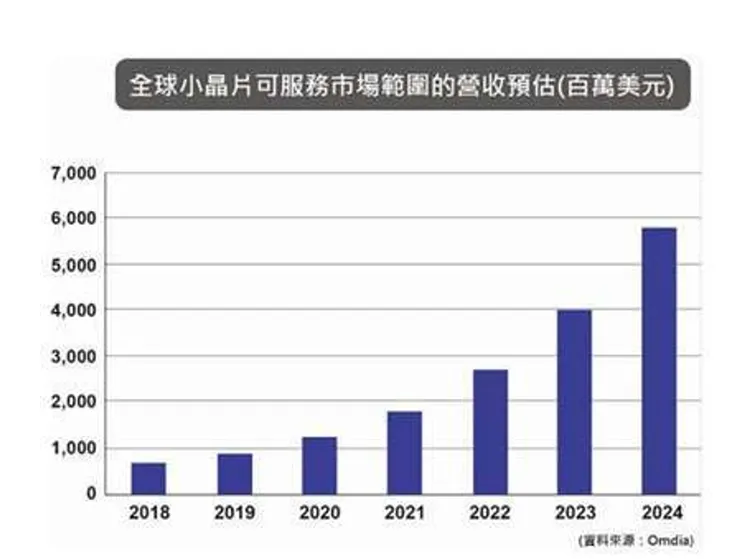

全球小晶片市場營收預估圖表(來源:Omdia)

根據英國產業諮詢公司Omdia,小晶片市場規模於2024年將達到58億美元,2035年則可超過570億美元,2024-2035十年之間有望成長將近10倍。全球領先的半導體公司如台積電、Intel、和三星等皆積極研發中。

淺談 Chiplet 小晶片技術

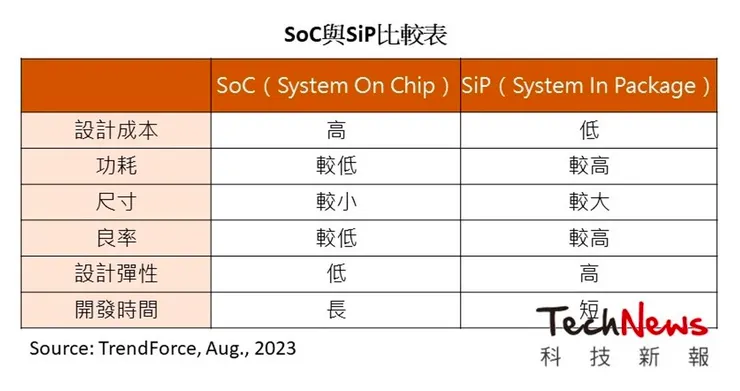

了解 Chiplet 技術的發展和影響,首先需要區分三個核心名詞:SoC、SiP、和 Chiplet。

SoC(System on Chip):將多個功能整合在同一製程工藝的晶片中

SiP(System in Package):通過異質整合技術,將使用不同製程工藝的晶片連接在同一封裝中。

Soc與Sip之比較圖 (來源:科技新報)

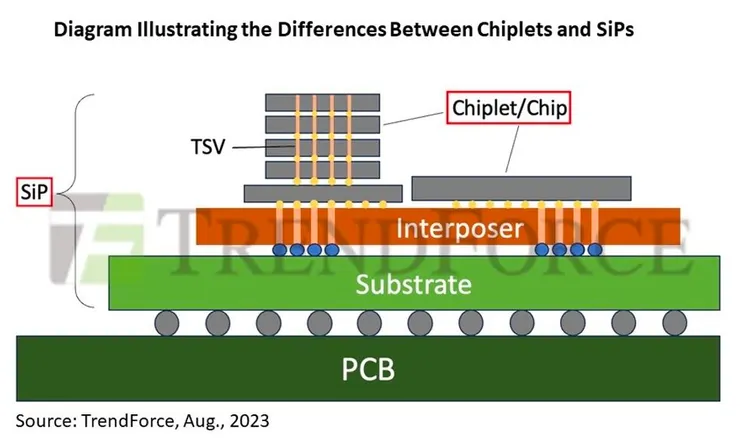

Chiplet 小晶片技術

同質與異質整合是小晶片的兩大技術。相較於傳統大晶片SoC,同質整合將其切分成數個小晶片,再運用高階晶片整合技術結合,此策略旨在提升先進製程的晶片良率,儘管需要額外的異質整合費用,但相對於高價的先進製程,總成本仍得以節省。另一方面,異質整合結合了不同功能的晶片(例如邏輯與記憶體晶片等),因這些晶片無法在同一製程下生產,故需利用高階晶片整合技術,來提高整體效能。蘋果電腦的 M1 Ultra 處理器就是採用了小晶片技術,效能不遜色於Intel 或AMD的晶片。

Sip封裝技術與Chiplet 圖示

Chiplet技術:突破禁令的關鍵?

Chiplet 技術具有多種優勢。首先,Chiplet 技術可以提高晶片的良率,因為使用小晶片降低了整體的晶片面積,減少了缺陷導致整顆晶片報廢的風險。再者,Chiplet 技術降低了設計的複雜度和成本,不同功能的小晶片可以使用各自最適合的製程,使各晶片獨立優化,從而獲得更好的整體性能。Chiplet 技術能夠提高設計彈性、縮短研發工時、降低成本,並增加晶片功能,它被認為是未來半導體製程的關鍵。

美國自2019年開始向中國實施半導體禁令,全面圍堵中國先進製程,2021年時,中科睿芯為發展伺服器晶片,與台廠金麗科合作使用Chiplet技術,將小晶片堆疊,運用12奈米製程做出了8核心,32位元的處理器,使得該系統無需依賴美製處理器,大幅提高了自製率,初步突破美國封鎖。

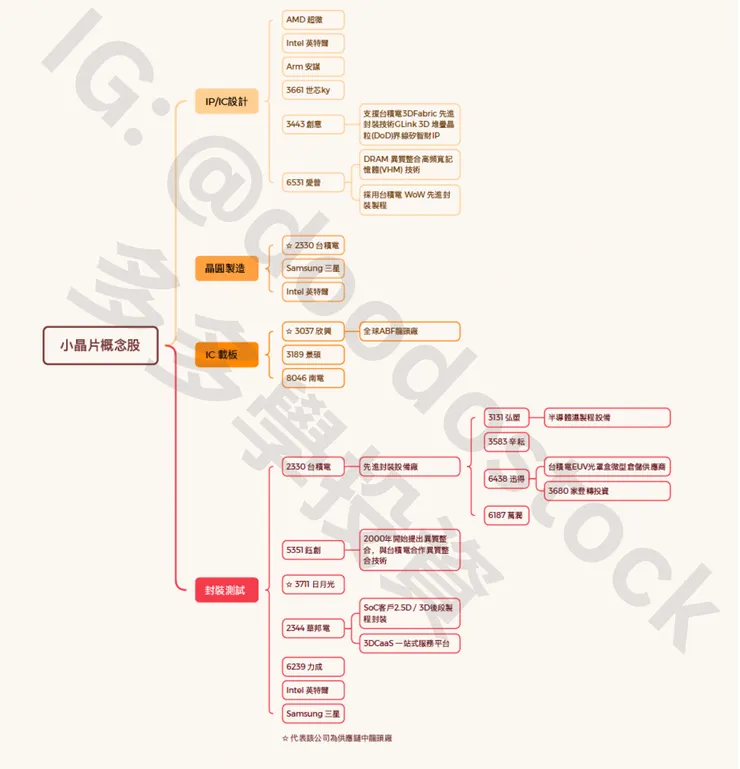

小晶片概念股

針對小晶片的發展,大廠如 Intel、台積電、三星、AMD、Microsoft、Google 和3711 日月光等 已共同推進 UCIe 小晶片聯盟(Universal Chiplet Interconnect Express),旨在標準化小晶片的資料傳輸架構,降低先進封裝設計的成本,為未來高效能運算晶片的主要技術平台。

小晶片心智圖 IG:@doodostock 多多學投資

小總結

隨著摩爾定律逼近其極限,小晶片(Chiplet)技術正迅速崛起為半導體業界的新方向。從其驚人的市場成長潛力到各大半導體巨頭的投入,都證明了其在未來技術發展中的關鍵地位。此外,透過業界的合作和共同努力,Chiplet技術將繼續革新半導體設計,帶領產業邁向新的里程碑。

參考資料及免責聲明