sync rst 和 async rst reg 在rtl上只有差在always block的condition不同,但是在合成上卻是兩種不同type的register,有著不同的優缺

sync reset reg :

always @ (postedge clk) begin

if (!rst_n) begin

a <= 0;

else

a <= input;

end

end

async reset reg :

always @ (postedge clk or negedge rst_n) begin

if (!rst_n) begin

a <= 0;

else

a <= input;

end

end

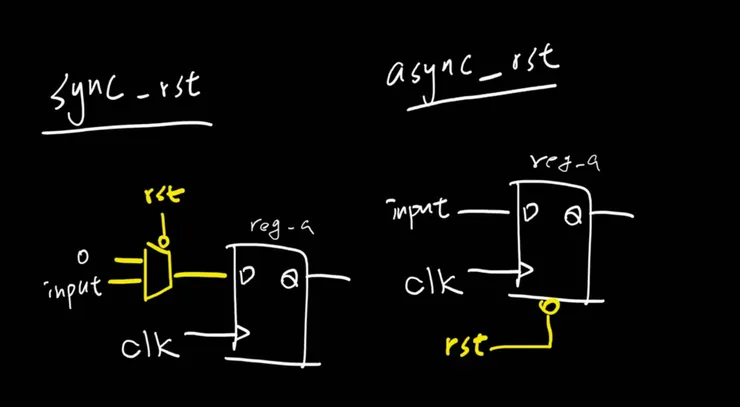

對於sync reset 而言,合成出來的結果是一個reg D in前接一個mux,

mux會由rst訊號來決定選0或是input作為D的輸入.

對於async reset而言,合成出來的結果是一個多一根reset pin的reg,

藉由這隻reset pin的trigger直接把reg洗成default vaule.

對於這兩種reg type有甚麼差呢?

作為面試答案的話可能有下面幾點比較

async reset :

- rst_n訊號assert時,當reg收到rst_n=0時,就會開始把reg設定回reset vaule,較即時

- 回復reset value不需要clk的介入,無時無刻都屬於可控狀態

- Area 較小

- 當reset wire 出現glitch或noise時抵抗力較差, 如果有一個glitch打出到reg reset pin上,value會瞬間reset掉導致function出現錯誤 <- 有甚麼方法可以盡量避免glitch的影響?下集介紹

- reset 訊號沒介入data path的timing,對於setup/hold time check較容易收斂一些

- 長reset tree難度較高 <- 甚麼是reset tree和一般討論的clk tree有甚麼不同?下集介紹

sync reset :

- rst_n 訊號assert需要維持較久,須等到reg收到clk postedge trigger時,reset vaule才會生效

- rst_n的功能需要有clk才能生效,module會有先天上的限制,在沒有clk前是無法做reset的,對於有clk gating的電路,假如發生系統reset時會沒有clk讓reg清回reset value

- Area 較大

- 抵擋reset wire glitch能力較強,glitch出現同時必須配合clk碰到edge trigger的剎那,發生機率較低

- reset 訊號介入data path的timing,對於setup/hold time check時必須綜合考慮reset對於timing的影響

- reset tree在先前修setup/hold time check時已經和clk tree解過timing問題,長reset tree容易

面試官回頭思考一下,

了解了上述優缺點,答案非常精闢漂亮,

很滿意地問了下一題,在寫design時要怎麼去挑選要用哪種type的reset?

...

..

.

對於這個問題來說,