前面探討完setup time / hold time violation的原因跟解法,

來更進一步探討一下現實面,

實際ic design中,

我們有可能會碰到一個狀況,

synthesis過後path出現了setup time violation 或 hold time violation,

但離tape out的時辰不遠了,

在沒辦法完全解乾淨眼前的violatoin的情況下,

要如何做仲裁,哪些是重要的不解的話可能帶來的impact又是如何?

有沒有其他的方式來做workaround?

這邊來分享一下我個人的見解供大家參考看看

對於setup time violation來說

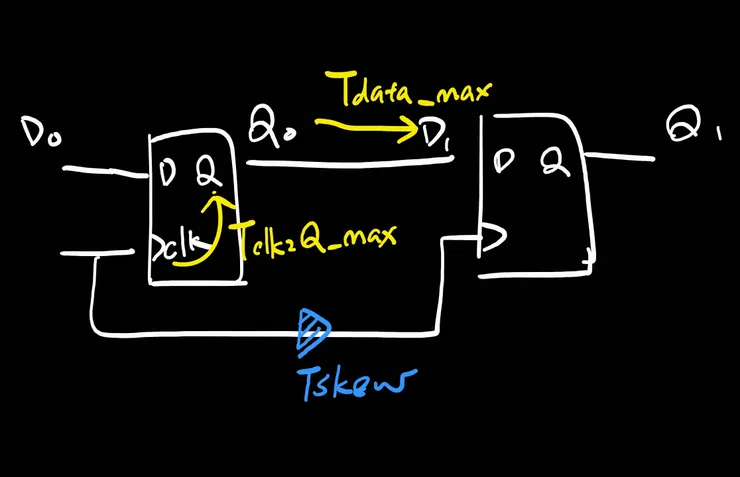

先來複習一下傳統的STA check formula

Tcycle + Tskew >= Tclk2Q_max + Tdata_max +Tsetup

公式意涵為

左半部為clk走到終點的速度

右半部為data最晚走到終點的速度

clk 走到終點前,data必須已經到了 則可以看到meet的timing

反之則violation

因此,有了這個感覺後來想一下,

假如我在synthesis過後setup time violation還是解不掉

會導致甚麼impact

從實際應用面來說,