準備實作Async Fifo時,

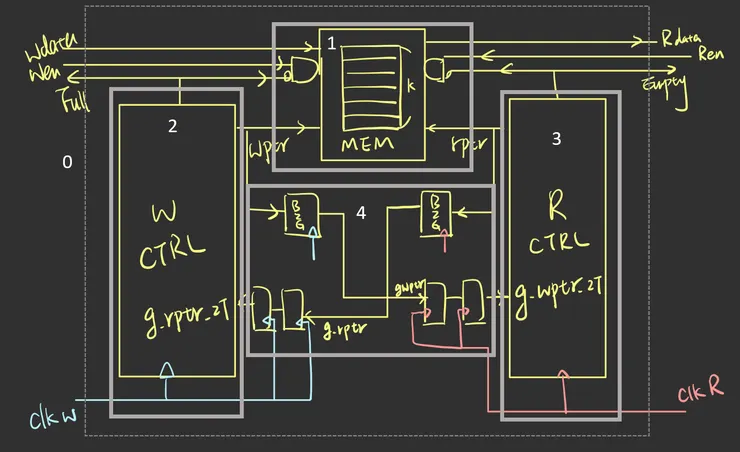

我習慣將整個架構切成4塊來實作,

讓coding實的思緒比較有條理一點.

Block 0 : 整體的interface

Block 1 : mem周邊

Block 2 : Gray code pointer control

Block 3 : write controller

Block 4 : read controller

Block 0 : async fifo intf

module asyc_fifo # (

parameter width = 8 , // wdata bits

parameter depth = 8 // mem depth k

)

(

input clkw, // write clk

input clkr, // read clk

input rst_nw, // write rst_b

input rst_nr, // read rst_b

input [width-1 : 0] wdata,

output reg [width-1 : 0] rdata,

input wen, // write enable

input ren, // read enable

);

Block 1 : mem peripheral

如果mem是sram的話可以不用rst訊號, reg則可有可無,這個論述就留給大家思考思考

write : wen觸發且full未達標時,可將wdata寫入mem中的wptr位置上 (write clk)