長鑫存儲(CXMT)是中國唯一量產DRAM的廠商,總部位於合肥,專注DDR4、DDR5與HBM技術研發。

過去五十年,中國多次嘗試進入動態隨機存取記憶體(DRAM, Dynamic Random Access Memory)市場,卻屢屢失敗。從北京大學早期的研究,到無錫華晶、再到中芯國際(SMIC, Semiconductor Manufacturing International Corporation),每一次努力都止步於商業化之前。直到長鑫存儲(CXMT, ChangXin Memory Technologies)的出現,中國才真正有了能挑戰三星(Samsung)、SK 海力士(SK hynix)與美光(Micron)的可能。

(延伸閱讀:記憶體世代演進:DRAM、Flash 與 HBM)從失敗到長鑫存儲的誕生

CXMT 的董事長朱一明。他是創辦人之一,兼具有技術設計與商業敏銳度,曾經在 GigaDevice(兆易創新)帶領設計與市場。

中國的 DRAM 追趕歷史可以追溯到 1970 年代,北京大學團隊在矽閘 NMOS 上製作出 1K 晶片,但始終落後世界一至三年。後來的無錫華晶在 256K 產品世代陷入危機,中芯國際在 2000 年代短暫量產 DRAM,最終因價格崩盤與台積電訴訟退出。這些失敗說明了單靠國家資金或短期技術轉移並不足夠。

真正的突破來自合肥。2016 年,地方政府啟動「506 專案」,投入超過 70 億美元,並拉攏兆易創新(GigaDevice, 中國領先的 NOR Flash 與微控制器設計公司)。兆易創新的創辦人朱一明,既有清華背景又在矽谷歷練多年,讓這個計畫有了技術與資金的雙重支撐。長鑫存儲成立後,更大規模從台灣與韓國挖角整個團隊,給予三至五倍薪資,快速補足研發與製造能力。

DDR4 與 DDR5 的追趕

在全球市場上,三星 2012 年展示 DDR4(Double Data Rate 4,同步動態隨機存取記憶體第四代),2014 年量產;SK 海力士與美光也在同時期加入。相比之下,長鑫存儲直到 2019 年才推出首款 DDR4/LPDDR4X(Low Power DDR4X,低功耗版本,常見於手機與筆電),基於 19 奈米製程,落後領先者約 5 至 7 年。但關鍵在於,它能穩定出貨並進入小米與傳音的供應鏈,避免重蹈福建晉華因制裁倒閉的覆轍。

2021 年,三星與 SK 海力士開始量產 DDR5(Double Data Rate 5,第五代),分別推出 DDR5-6400 與 DDR5-7200 產品,採用 D1a(10 奈米級,含 EUV 微影)製程。而長鑫存儲在 2024 年底推出 DDR5,雖然僅採用 1z node(約 15–16 奈米,未用 EUV),但仍將落後差距縮小到 3 至 4 年。更重要的是,CXMT 在單位密度上達到 0.239Gb/mm²,高於韓國同世代產品,顯示其製程優化能力已不容小覷。

中國的 HBM 戰略

隨著人工智慧(AI, Artificial Intelligence)與高效能運算(HPC, High Performance Computing)的興起,記憶體帶寬成為瓶頸,高帶寬記憶體(HBM, High Bandwidth Memory)成為關鍵解法。

長鑫存儲已於 2024 年下半年開始少量生產 HBM2,雖然世代上落後,但至少踏出關鍵一步。更長遠的目標是 2026 年量產 HBM3,並在 2027 年推出 HBM3E。這與韓美廠商的最新進度相比仍有差距,特別是在極紫外光微影(EUV, Extreme Ultraviolet Lithography)與先進封裝技術(如台積電 CoWoS, Chip-on-Wafer-on-Substrate)上的缺失,將直接影響良率與產品性能。

(延伸閱讀:馮紐曼瓶頸與 HBM:記憶體的架構挑戰)

4F² 單元結構:下一個突破口

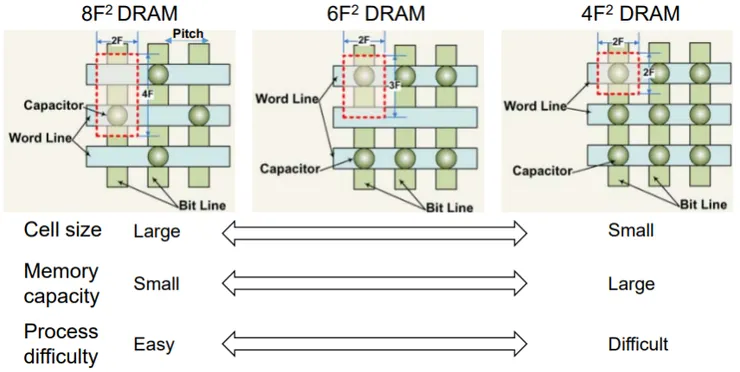

6F² 與 4F² 結構的截面示意,部分電容、通道(capacitor / channel)等元件形狀與間距變化。

目前主流的 DRAM 單元設計採用 6F² 結構,其中「F」代表製程線寬,6F² 表示單元面積是最小特徵尺寸的六倍。這個架構自 2007 年以來已使用多年。若能推進到 4F² 結構,單元面積將縮小三分之一,等於同一晶圓能容納更多記憶體單元,大幅提升密度與降低成本。

但挑戰在於:電容縮小後儲存電量不足,容易受雜訊影響;單元間距縮短會導致干擾加劇;製程也需要新的元件,例如垂直通道電晶體(VCT, Vertical Channel Transistor)或全環繞閘極(GAA, Gate-All-Around)來維持性能。長鑫存儲在 2023 年發表的研究已展示 4F² 測試晶片,顯示他們正在探索未來世代,而不僅僅是追趕現有產品。

2024 年長鑫存儲市占率約 8%,預計 2029 年可提升至 12.5%,仍落後三星 38%、SK 海力士 27%、美光 19%。然而,這已是中國首次建立具備國際競爭力的 DRAM 與 HBM 供應商。若長鑫存儲能在 4F² 單元結構與垂直通道電晶體上取得突破,未來有機會在 DDR 與 HBM 的交錯發展中,打破韓美長期壟斷。