產業論述

一、記憶體

關於記憶體相信近期不用多做於贅述,DRAM及FLASH系列報價相繼上漲,幅度甚是驚人。許多國內外公司跳出來表示記憶體產能不足,供不應求,甚至有錢也買不到,已經形成一項趨勢,只要趨勢未變的情況下,我們依然可以大膽假設,且相關高階記憶體部分如HBM的成長率也因應AI資料中心及相關應用也逐步擴大之中。然而市場研調指出記憶體封測的CAGR為3%~6%,屬於相對成長力道較弱,但可以說已經為成熟市場,因此得留意景氣循環的風險。關於記憶體便不再贅述。

二、FOPLP

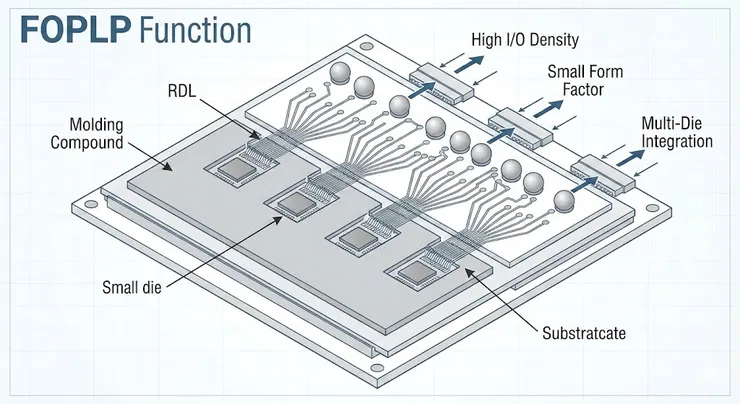

FOPLP,(Fan-Out Panel Level Packaging,扇出型面板級封裝),隨著摩爾定律放緩,半導體產業的戰場逐步從「把晶片做小」,轉移到「把封裝做好」。我們可以這樣認知,一塊板上我們期望東西塞越滿越好,效率更為高效,因此出現了FOPLP的封裝技術,面積利用率更高效,效率也更高,而成本更低。FOPLP 相比 CoWoS 具有成本優勢,是未來 AI 晶片、車用電子和高性能 Chiplet 整合的優選方案。介於傳統封裝與極致高階 CoWoS 之間,適用於對成本敏感、但要求高整合度的產品。

主要應用領域:

1.電源管理 IC (PMIC): 這類晶片用量極大,對成本敏感,且需要良好的散熱和電性導通能力,非常適合 FOPLP。車用 PMIC 是大宗。

2.射頻模組 (RF Modules): 5G/6G 手機或通訊設備中的射頻前端模組,需要整合多顆晶片且要求輕薄短小。

3.車用電子與感測器: 汽車電子化程度提高,需要大量可靠且成本合理的封裝晶片(如雷達、LiDAR控制晶片)。

4.物聯網 (IoT) 與穿戴式裝置: 需要極致輕薄的體積,FOPLP 可以實現高整合度的系統級封裝 (SiP)。

5.未來潛力:AI 與 HPC (高效能運算):這是一塊大餅。雖然目前頂級 AI GPU(如 NVIDIA H100)仍使用昂貴的 CoWoS,但隨著「Chiplet(小晶片)」趨勢發展,未來的 AI 加速卡或次旗艦產品,可能會採用「FOPLP 將多顆 Chiplet 整合在一塊大基板上」的方案,以達到效能與成本的平衡。AMD 傳出正在積極評估導入此技術。

1. 比較表格:FOPLP vs. FOWLP(台積電現使用)

圓形 方形/矩形

通常為 12 吋 (約 300mm 直徑) 很大,例如 600mm x 600mm

面積利用率 較低 (約 85% 以下) 極高 (可達 95% 以上)

生產效率 中高 極高

生產成本 較高 較低 (可降低 30%-40%)

成熟度 高 (台積電已大量量產) 中 (量產初期導入階段)

挑戰 成本較難再壓縮 設備標準尚未統一

1.未來展望 :

FOPLP 的預估年均複合成長率 (CAGR)?根據權威半導體市調機構 Yole Group 與各大研調機構的數據,這是一個高成長賽道,但基期較低。

整體扇出型封裝 (Fan-Out Packaging) 市場: 預計 2024~2028 年的 CAGR 約為 15% - 20%。

FOPLP (面板級扇出型封裝) 專項市場: 由於是新興技術,基期低,成長率更高。預計未來 5 年的 CAGR 可達到 30% - 40%。

註:這比傳統半導體產業(約 5-8%)高出許多,屬於「高成長」類別。

2.產業風險 : FOPLP 技術雖然先進,但目前很多廠商(封測廠、面板廠、載板廠)都在做,標準尚未完全統一,技術壁壘雖有但競爭激烈,這意味著尚未形成「贏家通吃」的壟斷局面,而良率也是將來廠商會遇到之相關問題。

- (註:Substratcate需更正為Substrate)

FOPLP 的基本組成:- Small die(小晶片): 裸晶被放置在其中。

- Molding Compound(塑封料): 將晶片包覆固定住,形成一個重構的表面。

- RDL (Redistribution Layer,重佈線層): 這是最重要的部分。圖片精準地畫出了細小的線路從晶片上方「扇出(Fan-Out)」連接到較大的外部錫球(Solder Balls)上。這正是「扇出型封裝」的定義。

- 功能與優勢標示正確: 圖中右側的三個箭頭精準地指出了 FOPLP 的用途:

- High I/O Density(高 I/O 密度): 透過 RDL,小晶片也能擁有大量的對外連接點。

- Small Form Factor(小型化/輕薄化): 省去了傳統笨重的基板和打線,使封裝體積變小變薄。

- Multi-Die Integration(多晶片整合): 圖中明確展示了多個晶片被封裝在同一個結構中,這呈現了異質整合(如 SiP)的能力。

免責聲明(Disclaimer)

本內容僅為本人基於公開資訊所做之個人觀點與研究分享,不構成任何投資建議、投資邀約、推薦或勸誘。文中所提及之市場看法、標的分析及相關預測,均可能隨市場環境變化而調整,不保證其完整性、即時性或正確性。投資具有風險,過去績效不代表未來表現,任何投資決策均應由投資人自行評估其風險承受能力,並自負盈虧。