從1965年由 Fairchild 創辦人之一 Gordon Moore 所提出的預測每年晶片上的元件數量將倍增開始,我們的世界就在這條曲線上迅速前進,成為半導體產業的圭臬。這不只是技術進步的象徵,更是一場單位成本的核心邏輯:同樣價格,效能翻倍;同樣功能,價格再降。經過60年,這條曲線已然變形,甚至出現分裂與反彈。但它沒有終結,反而在三個維度上展現出轉生:1. 密度提升(Scaling Up)、2. 成本下降(Scaling Down)、3. 功能擴散(Scaling Out)。

摩爾定律 1.0:從實驗室到黃金年代的密度提升(Scaling Up)

年《Electronics》雜誌,Gordon Moore 預測10年內可在單晶片上整合超過65,000個元件。1975年他再度回顧並指出這一發展可歸因於三項要素:晶片面積放大、線寬縮小,以及電路設計巧思(device cleverness)的進步。

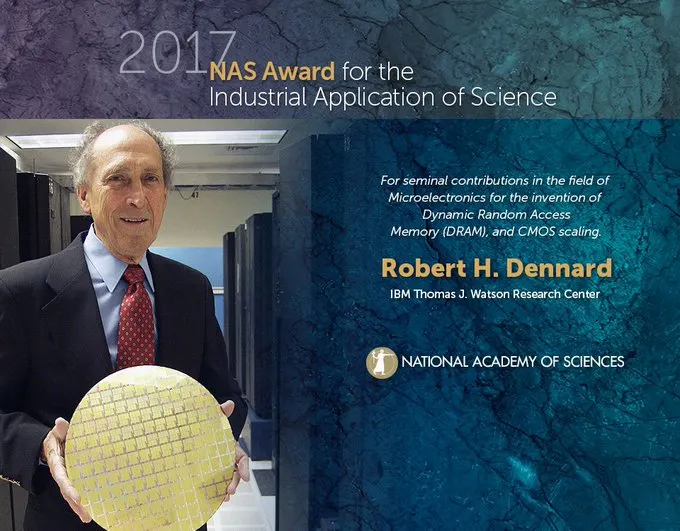

Robert H. Dennard 「現代記憶體之父」,1967 年,Dennard 在 IBM 發明了單晶體 DRAM 結構,這種結構只需一顆電晶體和一個電容,就能儲存 1 bit 資料。

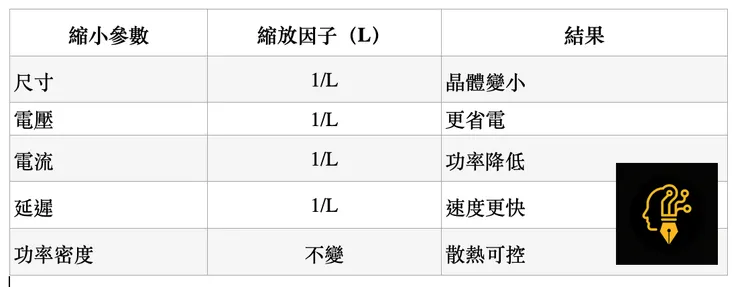

1974 年,IBM 工程師 Robert Dennard 提出一套晶體縮小的黃金法則,後來被稱為 Dennard Scaling。這項規則指出,只要電晶體的尺寸、電壓與電流等都以相同比例縮小,其效能會更快、功耗會更低,而功率密度則維持穩定。

這使 1975–2005 年成為摩爾定律的黃金期:每一個世代的電晶體縮小,都能無痛帶來效能與價格的進步,甚至成為縮小就是進步的代名詞。但進入 21 世紀後,隨著電壓難以再線性下降,Dennard Scaling 終止。晶片開始產生嚴重的漏電與熱功耗問題,導致主頻停滯、核心數提升遇阻,整個半導體產業被迫從快就是好轉向其他設計取向。

摩爾定律 2.0:當微縮不再等於進步,成本主導一切(Scaling down)

電壓難以隨尺寸同步縮小,導致漏電與功耗劇增。主頻停止提升(卡在 2~3GHz),摩爾定律由效能提升轉向成本降低的邏輯。

- 每年降低 30% 的單位電晶體成本

- 讓更多產品(如洗衣機、玩具、溫控器)得以內建計算力

這個階段的成功關鍵不在更好的晶片,而是夠用且更便宜的擴散式應用。然而,到了 5nm 世代,第一次出現價格反彈。EUV 設備昂貴,導致每個電晶體的成本不降反升。摩爾定律似乎失靈了。雖然後來扭轉了頹勢,證明摩爾定律的經濟邏輯仍能延續,只不過必須付出更多資本與系統設計整合的代價。

摩爾定律 3.0:Scaling out

如今,真正推動摩爾定律續命的關鍵是整合與擴散

- 利用先進封裝(如 TSMC CoWoS、Intel Foveros)進行 3D 整合

- 將感測器、記憶體、模擬電路整合進單一模組

- 發展異質運算與多晶粒協同架構

摩爾定律從晶片製程的戰場,轉向系統整合的舞台。這也催生 Intel 的 IDM 2.0(整合元件製造商)策略:設計團隊可以使用 TSMC 的先進製程,而製造端必須重新競爭、自證價值。這象徵著一種自我去整合化,將摩爾定律推進的責任分散到整個價值鏈中。

摩爾定律的經濟學

摩爾定律的核心是經濟定律。早期透過 Dennard Scaling 可以同步縮小晶體管尺寸與電壓,達成效能提升與功耗下降的雙贏,但當電壓再也無法下降後,縮小不再帶來好處,反而提高成本。那為什麼還要繼續縮?