面對台積電在 3nm 製程上的領先優勢,Intel 不再單純以製程節點競爭,而是積極將自身長年累積的封裝技術商品化,其中最具代表性的正是 EMIB(Embedded Multi-Die Interconnect Bridge),以及與之搭配的 3D 封裝技術 Foveros。

當 EMIB 是晶粒間的橋,Foveros 是上下連接的樓層,玻璃基板則是撐起整座建築的地基。

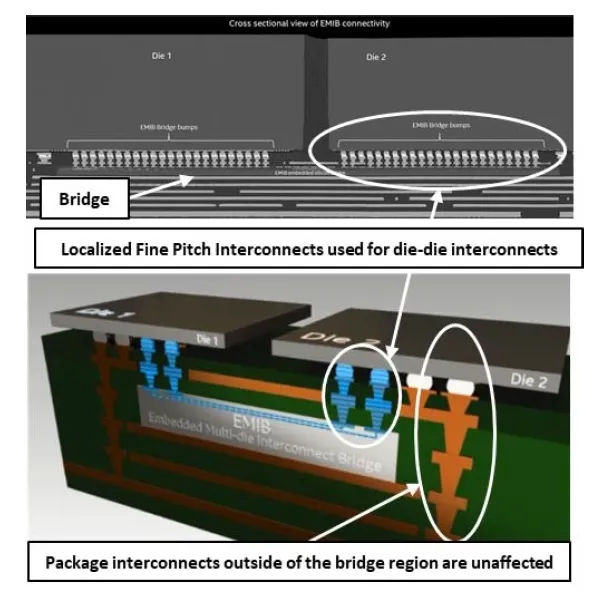

EMIB 是什麼?

EMIB 技術透過嵌入封裝基板的橋接區域,實現多晶粒高速互連。

這種設計讓不同功能模組(CPU、GPU、IO、記憶體)可分別以最適合的製程製造,再透過封裝階段進行整合,大幅提升製造效率與系統整體效能。

Foveros 是什麼?

Foveros 是 Intel 的 3D 封裝技術平台,主打異質晶粒的垂直堆疊。下層 base die 通常負責電源管理與快取,上層 compute die 負責邏輯運算。兩者透過 TSV(穿矽通孔)與 micro-bump 互連,未來版本將採 hybrid bonding 以提升頻寬與降低延遲。

Foveros 的設計自由度極高,讓不同功能晶粒可使用不同製程製造,並在封裝階段整合成單一 SoC。這不僅提升系統效能,也有助於加快產品設計週期。Intel 亦強調 Foveros 的 power delivery 與熱管理優勢,結合專用低電阻 TSV 技術,可顯著改善高功耗晶片的供電效率,這對資料中心與邊緣 AI 裝置至關重要。

補充一點有趣背景:Foveros 這個名字來自希臘語「φοβερός」,原意為「驚人的、卓越的」。這不只是命名巧思,也反映 Intel 對此項技術作為未來封裝基礎平台的高度期待與雄心。

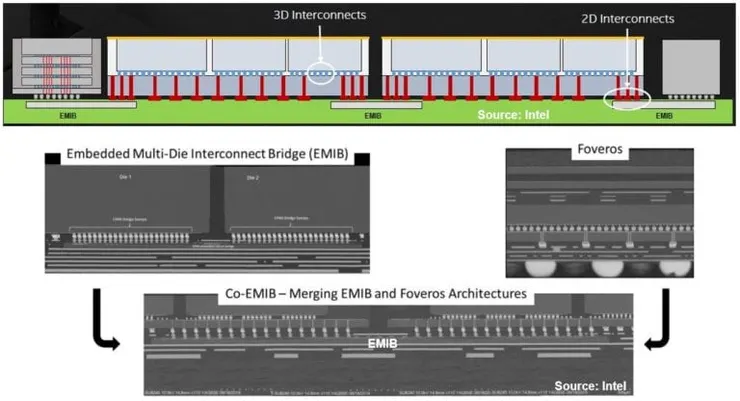

EMIB × Foveros:橫向與垂直的互補組合

為進一步擴展封裝整合邊界,Intel 推出 Co-EMIB 技術(Complementary EMIB)。這項技術允許多個 Foveros 堆疊模組在同一封裝基板上進行互聯,並透過多個 EMIB 橋接實現系統級整合(System-Level Integration)。

而 Co-EMIB 背後的核心理念,正是 ODI(Omni-Directional Interconnect,全向互聯)。ODI 並非全新材料或封裝工法,而是將 EMIB(2.5D)與 Foveros(3D)的互聯邏輯整合成一種更加自由彈性的「封裝內互聯網路」。

ODI 的價值在於,它允許 chiplet 在任意方向彼此通訊,使設計師不再受限於晶粒位置排布。這種全向互聯的網狀結構,打破過去點對點、固定方向的設計邏輯,是支撐 Co-EMIB 等大型異質系統封裝的關鍵抽象層。

舉例來說,在 Ponte Vecchio 中,Intel 使用 Co-EMIB 技術整合超過 40 個 chiplet,結合 EMIB 的矽橋與 Foveros 的 3D 堆疊,完成高度模組化的超級運算平台。這種系統級封裝模式,讓多個邏輯與記憶體模組能分散配置卻保持高度協同。

此外,Co-EMIB 的發展也同步考量後續熱傳導與電源供應挑戰,透過分層電力分配與精密熱設計,確保高功耗模組在高密度封裝下仍具穩定性。

與台積電 CoWoS 的對決:成熟 vs 模組化

在封裝領域,台積電的 CoWoS(Chip-on-Wafer-on-Substrate) 是市場主流。其設計以大面積矽中介層為基礎,支援高頻寬記憶體(如 HBM)與大量晶粒整合。NVIDIA、AMD、Apple 等高階晶片幾乎都採用 CoWoS 平台。

然而,這種設計成本高、彈性低,限制了晶片模組化與重複利用的可能性。相比之下,EMIB 的局部橋接方式 可針對不同設計需求彈性調整,搭配 Foveros 的垂直結構與未來的玻璃基板支持,Intel 正試圖建立出一個真正模組化、可擴展的封裝生態。

但目前最大的挑戰仍在於:Intel 封裝雖具備技術潛力,卻尚未建立起足夠規模的客戶採用與供應鏈配套。反觀台積電的 CoWoS 已與日月光、SK Hynix 等形成封裝供應體系,市佔率優勢明確。