想要跨入Verilog的領域時

總是發現好像不像c code一樣有滿滿的資源

對於新手來說必須要先了解甚麼是design甚麼又是testbench

要怎麼在tesebench中產出stimulate及比對最後output的bit ture

可能在很多人想跨入時,發現這個的門檻極高,就直接放棄惹

因此在這邊推薦大家一個很優質的coding練習平臺,

完全免費,由淺入深的題目,讓大家慢慢熟悉整個Verilog的語法

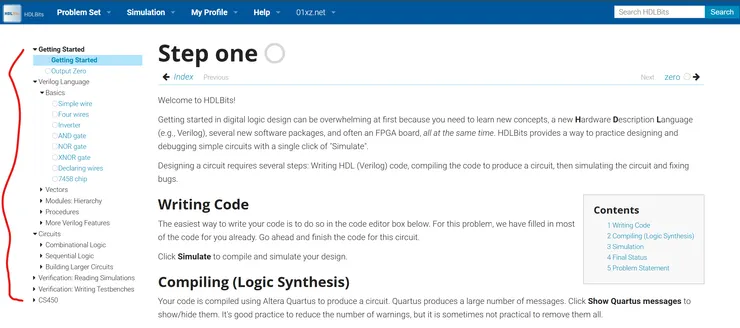

HDLbits

https://hdlbits.01xz.net/wiki/Step_one

大家進入網頁後,

每個章節的內容會列在左手邊,

對於verilog還不熟悉的朋友可以藉由網頁的引導一題一題往下寫,

每章的開頭都會有教學指引,可以看懂說明後搭配例題練習

選好題目後,相關的說明及coding的位置往下滾就會看到了

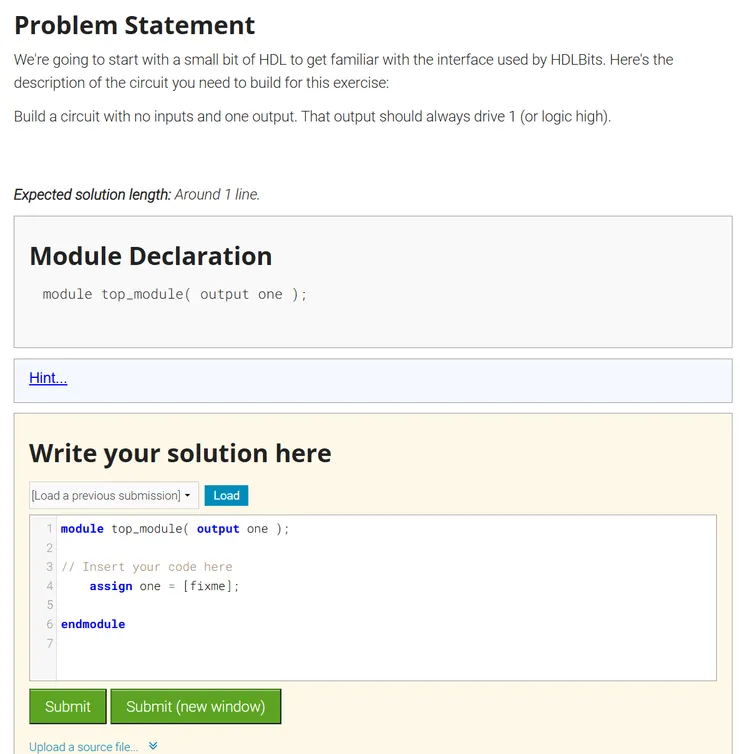

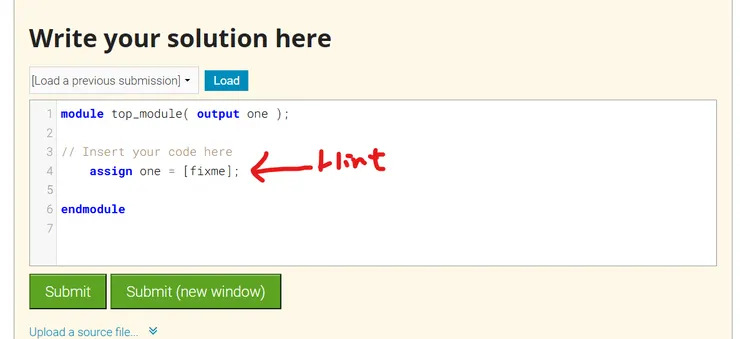

以上述為例 Step one的題目

Problem Statement中提到

Build a circuit with no inputs and one output. That output should always drive 1 (or logic high).

這題希望作一個沒有輸入的module,但是他有一個output alway 推1

對於ic design中時常用到的一個功能,

寫一個 tie cell的function

這個function只有兩種type , tie 1或tie0

在follow這個hint後可以推出預期的答案

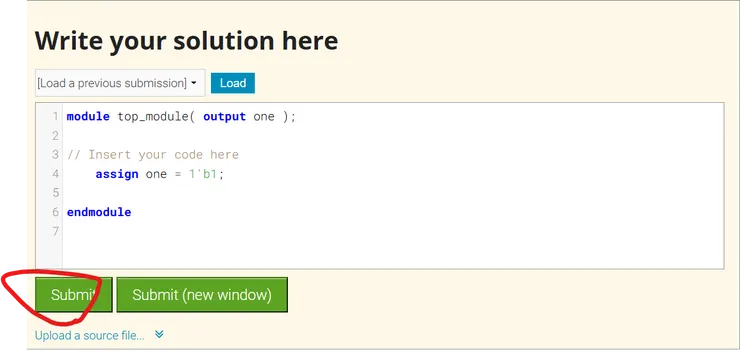

寫完後即可submit,

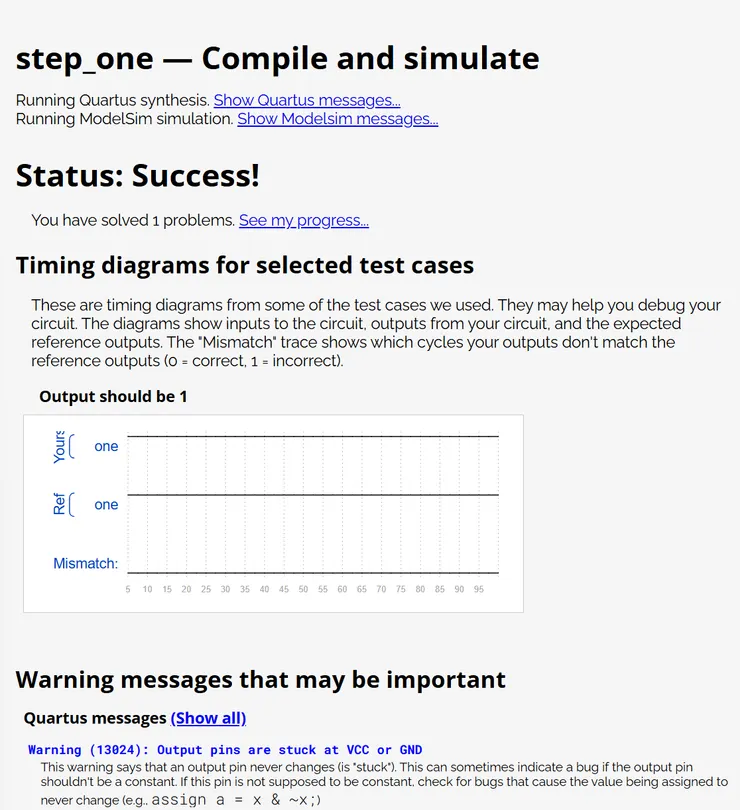

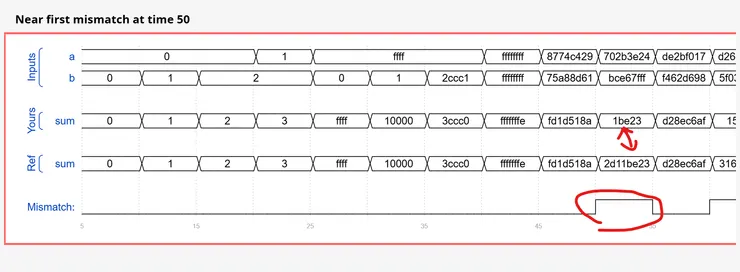

跑完compile和simulation後就會提供Status以及test case的waveform

如果有Compile error 會於log中告知 大部分都是屬於synthex error

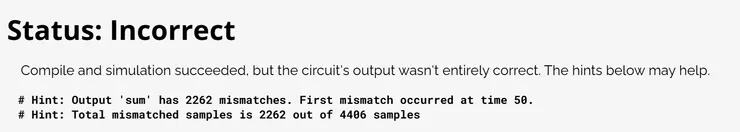

Incorrect怎麼辦?

碰到incorrect最直接的解法就是去查waveform,

利用input去推敲為甚麼我產出的output和reference是不一致的

不過由於平臺中不是每題都有提供solution,

如果有些問題想不到怎麼解的話,

可以來參考出一張嘴 入門找手感系列,

這邊會和大家一起刷題,提供我的解法讓大家參考討論

Digital IC designer 兩大核心缺一不可 Verilog Coding , Design Concept

Verilog像是個工具幫忙作出想要的功能,

但post silicon中功能還要能動,相關的design concept不可少