CoWoS(Chip-on-Wafer-on-Substrate)是目前最成功的先進封裝平台之一。從高階 AI GPU 到超大算力模組,幾乎都依賴這項技術,透過中介層整合多顆晶片與 HBM 記憶體,形成高速、高頻寬的運算封裝系統。然而,隨著 AI 晶片越做越大,HBM 整合需求越來越多,CoWoS 的物理限制也開始浮現。晶圓是圓形的,而封裝需求是擴展的。光罩尺寸有限,導致單一封裝可處理的範圍無法再進一步放大。而散熱、良率、成本等因素,也逐步拉緊這條技術邊界。

更進一步,AI 計算平台的需求已經從單顆超大晶片,轉向多顆模組的高速互聯。這意味著封裝技術不只是要塞下更多的晶片,更要讓每一顆晶片彼此之間能高速溝通、有效散熱、方便驗證。因此,CoPoS 被提出,並不是要取代 CoWoS,而是讓封裝設計從單一封裝邏輯,轉向模組化、面板化,邁入一個更具延展性與產能彈性的時代。

CoPoS 為何而生?

CoPoS( Chip-on-Package-on-Substrate),是一種模組封裝平台架構。與其讓所有晶片直接貼附在中介層上,不如先把不同功能的晶片組成一個個模組,預先完成封裝、測試與整合,再把這些模組依照設計需求配置到一塊大型基板之上。

這種方式讓封裝流程變得更有彈性、更容易分工。每個模組可以在不同階段、不同據點完成封裝與驗證,最後再統一整合。而整體封裝平台也從圓形晶圓的思維,轉向方形面板的布局,面積效率與產出規模同步提升。

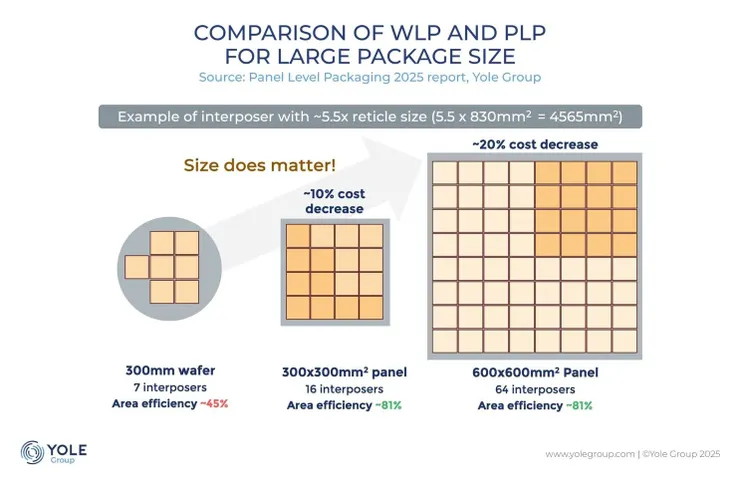

晶圓是圓的,而封裝模組與晶片本身往往是方形,導致圓形晶圓邊緣的空間難以完全利用。這不只是浪費,而是在高單價製程下對成本與良率的重大壓力。更根本的限制來自光罩尺寸,也就是 reticle size。現有光刻設備每次能曝光的區域有限,大約為 26 mm 乘以 33 mm。超過這個範圍,就必須分區多次曝光並拼接,這稱為 stitching。拼接雖然技術上可行,但會導致圖樣對位誤差上升、製程時間延長、良率下降,進而推高整體封裝成本。

雖然 chiplet 架構已經普遍,讓大型晶片的邏輯切分為多顆模組成為可能,但這些模組之間仍需透過一個整合平台連接,也就是中介層或 RDL 結構。這些結構依然需要透過光刻完成,因此仍無法逃脫光罩尺寸的天花板。當封裝系統整體超出單次曝光範圍,整體效率與成本就開始變得難以承受。

若從封裝製程效率來看,與其持續在圓形晶圓上堆高密度模組,不如直接轉向大型方形面板。這類面板的尺寸可以達到 500 毫米以上,單片封裝數量可大幅提升。每個模組也可透過區塊式管理與驗證,提高生產彈性與品質控管效率。這樣的封裝思維不只是空間擴張,更是流程的模組化。CoPoS 將封裝從連續的一體化製程,拆分為可重組的模組單位,讓整個封裝設計邏輯與製造模式產生質變。

現有封裝平台的延續與對應

CoWoS 在目前的應用中已經劃分出多種對應策略。根據目前主流 AI 與資料中心晶片的封裝選擇,可以清楚觀察到封裝技術的應用分層:NVIDIA 的 H100 與 H200 採用 CoWoS-S,代表標準中介層封裝結構;B200 與 B300 則因模組數與 HBM 整合需求上升,轉向面積更大的 CoWoS-L。Amazon 的 Inferentia 與 Trainium 系列則使用 CoWoS-R,顯示其封裝設計更偏向可客製的彈性整合。Broadcom 的 TPU、AMD 的 MI300 系列與 Intel 的 Gaudi2 與 Gaudi3 多採用 CoWoS-S。

從這些實際晶片的封裝選擇可看出,越往高端、越接近多顆 HBM 整合需求的產品,越傾向使用 CoWoS-L;而越標準化與量產導向的產品,則仍維持在 CoWoS-S。這些封裝仍舊基於晶圓與中介層的工藝思維。隨著封裝尺寸持續膨脹、模組需求日漸多元,這些架構正逐漸面臨空間限制與製程挑戰。

這也正是 CoPoS 被推動的時機點。CoPoS 並不是推翻這些架構,而是提供一種以模組封裝為核心、面板平台為基礎的設計選項,能支援更彈性的組合、更大的封裝區域,以及更好的測試與製程分離能力。它讓封裝從「晶片 + interposer」的一體化設計邏輯,轉向「模組 + 面板」的可組裝邏輯,是封裝策略在大規模 AI 世代的自然演化。

SoW-X 與 CoPoS 的架構對照

SoW-X(System-on-Wafer Extended)概念與 CoPoS 同樣在追求更大面積、更完整系統整合的目標,但方法截然不同。

SoW-X 是直接將一整個系統設計在 wafer 上,將邏輯、記憶體、互聯、甚至感測元件一體化整合,形成一塊超大型的系統晶圓。這種作法適合極高頻寬、極低延遲的特定應用,但對設計與製造技術要求極高,良率控管也相對困難。

CoPoS 則走的是模組化與拼接的思路,將每個子系統獨立處理後再進行組裝,整體彈性更大、導入風險較低,也更容易與現有製程接軌。

兩者並非對立,而是在不同需求場景下各自發展的封裝策略。未來甚至可能出現混合式架構,例如在 CoPoS 平台中組裝一塊 SoW module,讓模組化與一體化結合成為更高階的系統封裝平台。