一、原子模型

基本的原子模型是由質子、中子及電子組合而成,其中,帶正電的質子與不帶電的中子構成原子核,而帶負電的電子則分布於原子核外的各軌道中並受其束縛。

最靠近原子核軌道(第一圈)能容納2個電子,第二圈可容納8個電子,其規律為以下公式:

所以以此類推,第三圈可容納18個電子、第四圈可容納32個電子…

再來我們舉矽(Si)原子為例,其原子序為14,因為電中性,其電子數同為14,以內圈到外圈依序為2、8、4個電子,此時我們會稱最外層的電子為價電子,價電子的數量通常決定了該元素的性質,例如價電子數為1表示活性高(導體),而擁有8個價電子時,其穩定性最高(絕緣體),最後,通常我們所說的半導體,其價電子數量介於絕緣體與導體之間,通常為4個,例如剛剛提到的矽(Si)以及鍺(Ge)。

二、矽晶體結構

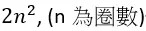

當矽原子彼此靠近時,價電子會互相作用,原子排列成規則結構。每個矽原子都與 四個最鄰近原子 形成鍵結,這四個鍵就是 共價鍵 (Covalent bonds)。

從上圖我們知道共價鍵是由兩個原子共享一對價電子形成的,在矽晶體中,每個矽原子有 4 個價電子,剛好與四個鄰近原子共享。

三、自由電子與電洞

未被原子核及共價鍵所束縛的電子稱為自由電子,而原本共價鍵因為價電子的脫離留下了多餘的位置,其稱作電洞。

價電子成為自由電子的條件為價電子必須獲得能量(如熱擾動或外加電場),使價電子由價電帶的能階跨過禁止帶而至傳導帶的能階上。而電子由價電帶至傳導帶所需最小能量稱為能隙。

通常,絕緣體的能隙大,其價電子不易跨過禁止帶,因而無法形成自由電子,也就無法導電 ; 導體則相反,其能隙極小甚至價電帶與傳導帶重疊,則導電性佳 ; 最後我們關注的半導體,其能隙小(大約1電子伏特, 1eV),通常施加熱擾動,價電子才可成為自由電子,故導電性較差。

四、本質半導體 (Intrinsic Semiconductors)

之前我們提過,當價電子因為熱能跳出共價鍵後,原本位置會留下「空位」。稱為 電洞。隨著溫度的升高,更多的共價鍵被破壞,產生更多的自由電子和電洞,並且電洞可能會吸引相鄰的自由電子重新復合,而此過程會造成另一電洞的產生,看起來像是正電荷在半導體中移動 (雖然電洞並非真正的粒子,但在電流分析中,可以想像成「正電荷在移動」)。

在半導體中,貢獻電流的有兩種載子:

- 自由電子 → 負電

- 電洞 → 正電

- 因此,半導體導電性來自於 電子–電洞對

沒有摻雜其他雜質原子的半導體,稱作本質半導體,如純矽,在這種材料中,電子與電洞完全由「熱擾動」生成。其特徵為: 電子數 = 電洞數 = 本質載子濃度 (intrinsic carrier concentration)。

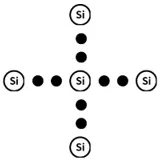

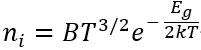

我們用ni來表示 本質載子濃度。其公式如下:

- B: 與材料特性有關的係數

- T: 溫度 (K)

- Eg: 能隙

- 𝑘:波茲曼常數,數值為86 X 10-6,單位是 eV/K