FIFO題目答得好不好可以直接看出面試者的程度為何,

FIFO看似簡單卻濃縮了非常多的design細節在裡面,

在這邊來和各位分享一下我個人的心得.

作為designer最常使用到的fifo就只有兩種屬性

1.sync fifo

2.async fifo

那這邊的sync或async指的是甚麼東西是否為同步呢?

評判的依據是根據write和read端所使用的clk是否來源是同步的.

如果是write/read使用同個source clk,

在STA分析時會被收斂timing則是屬於sync fifo的範疇.

如果write/read所使用的clk來自不同的source clk,

在STA分析時並無法確定timing使否meet則屬於async fifo的範疇.

當然這是屬於一個標準的分類法,

那我是否能在write/read的clk為sync的條件下使用async fifo?

抑或是在write/read的clk為async時使用sync fifo呢?

這樣混搭又會發生甚麼問題

值得好好思考一下

作為進階的面試考題

比起從正面論述何時要用sync何時用async

直接倒過來問用如果用錯會發生甚麼事情可以更了解一個面試者的思考

如果有辦法答出問題的話

想必對於sync或async的概念有著不錯的認識

那我們最後再回頭探討這個問題

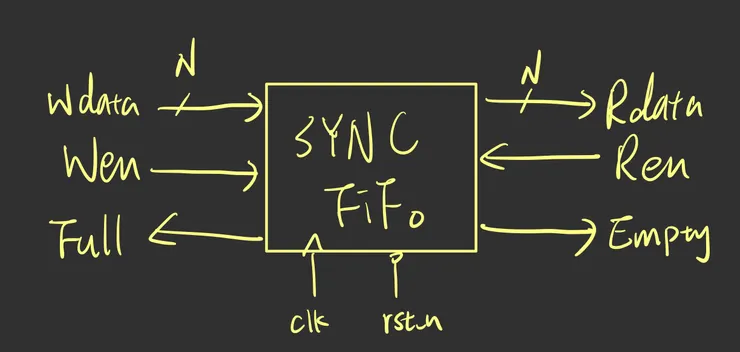

文章開始來介紹何謂 (1) sync fifo

Top view看起來像這樣

Interface 大致有

讀寫data用的Wdata/Rdata

寫入讀取有效判斷的Wen/Ren

告訴master或slave FIFO已經空了或滿了的Full/Empty

以及clk source 和rst_n

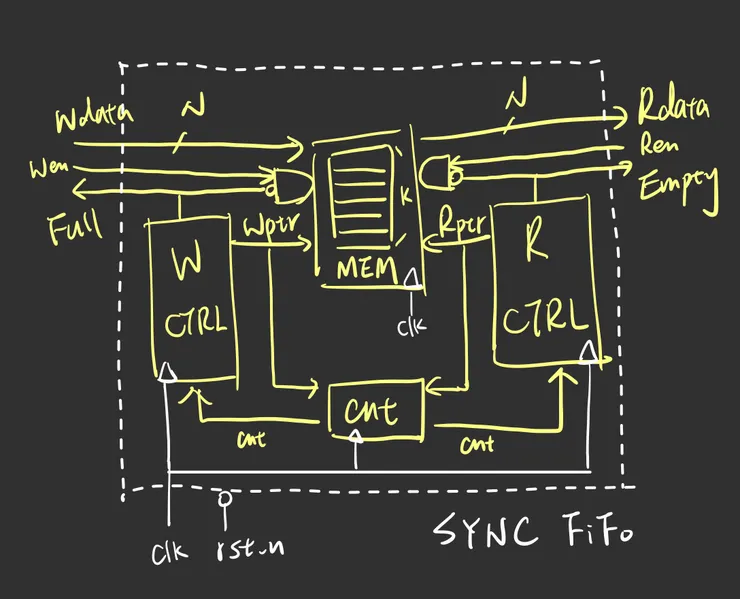

對於內部的細節展開為下圖

相信對於第一次接觸的人每次看到這張圖就放棄這題了,

然而這對於要面試的人來說是必經之路,

您只要放下心好好看完接下來的說明,

相信你就可以開始祈禱其他競爭對手會放棄這題了

為了避免這張圖內容一次太多

我拆解了幾個步驟,

大家在看懂後也可以跟著我的步驟畫一次這張圖,

大多時候面試時是需要自己畫出這些圖的.

(1) 主要的幾個function block