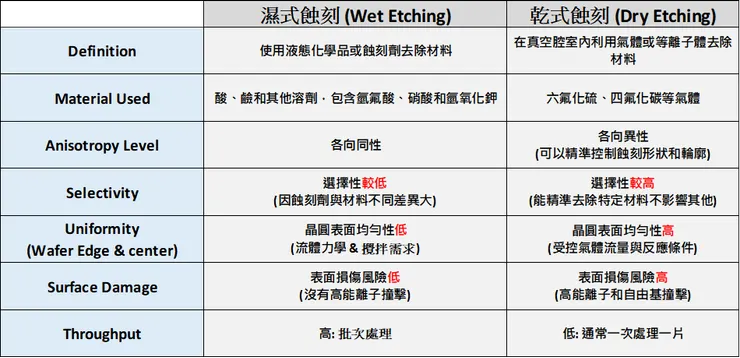

半導體製程蝕刻 – 乾式蝕刻 (Dry Etching) & 濕式蝕刻 (Wet Etching)

介紹一些乾式蝕刻的技術

1. Dielectric Etch(介電質蝕刻) 是為了在「絕緣層」中開路(挖垂直的洞)

「乾式蝕刻」技術,主要用於在晶圓表面的絕緣層(介電材料)上移除材料。

- 常用電漿: CCP (電容耦合電漿)

- 常見目標: 二氧化矽 (Oxide)、氮化矽 (Nitride)、低介電常數材料 (Low-k)

- 主要用途: 製作接觸孔 (Contact)、通孔 (Via) 或溝槽 (Trench),用來隔離電路

- 特性: 需要極高深寬比 (HAR),強調垂直向下的穿透力與對底層的高選擇比

- Lam 產品: Vantex & Flex 系列

2. Conductor Etch(導體蝕刻)是為了在「導電層」中造路(切水平的線)

「乾式蝕刻」技術,指蝕刻具導電性或半導電性的材料。

- 常用電漿: ICP (感應耦合電漿)

- 主要分支:

- Silicon/Poly Etch(矽/多晶矽蝕刻): 蝕刻矽基板或多晶矽,是定義電晶體閘極 (Gate) 的關鍵。

- Metal Etch(金屬蝕刻): 專門蝕刻鋁 (Al)、鎢 (W) 等金屬導線,需處理副產物造成的腐蝕問題。

- Silicide Etch(矽化物蝕刻): 蝕刻如矽化鎢 (WSi) 等用於降低電阻的複合材料。

- 常見目標: 多晶矽 (Polysilicon)、鋁 (Al)、鎢 (W)

- 主要用途: 製作閘極結構、電晶體源極/汲極連接、金屬導線層

- 特性: 極度強調關鍵尺寸 (CD) 控制,要求奈米級的精準線寬

- Lam 產品: Kiyo 系列

3. Atomic Layer Etch (ALE, 原子層蝕刻)

最尖端的「乾式蝕刻」技術,採取數位化、循環式的蝕刻方式。

- 技術原理: 表面改性與移除兩步驟循環,每次僅移除單層原子。

- 常見目標: 先進製程中的超薄膜層、極微小間距結構

- 主要用途: 用於 5nm 以下製程,解決 FinFET 或 GAA 結構中傳統蝕刻過於粗暴的問題

- 特性: 零損傷、方向性極致精準、厚度控制達到原子級

- Lam 產品: Panther 系統

4. Photoresist Strip / Ashing (光阻去除/灰化)

蝕刻製程後的必要配套技術,用於移除保護用的有機光阻。

- 常用電漿: 氧氣電漿 ( Plasma)

- 技術原理: 利用化學反應將有機光阻「燃燒」氣化為二氧化碳與水蒸氣。

- 常見目標: 已完成圖案轉移後的剩餘光阻 (Photoresist)

- 主要用途: 蝕刻後的表面清空(大掃除),確保下一層製程表面乾淨

- 特性: 強調去汙潔淨度,且不能損傷下方已經蝕刻好的精細結構

- Lam 產品: Versys (某些模組) 或專門的 Strip 設備

參考資料: Wet Etching vs. Dry Etching | Cadence & others